## Wafer Defect Prediction with Statistical Machine Learning

by

### Naomi Arnold

B.S. Industrial Engineering and Operations Research, UC Berkeley, 2009

Submitted to the Institute for Data, Systems, and Society and the MIT Sloan School of Management in partial fulfillment of the requirements for the degrees of MASSACHUSETTS INSTITUTE

OF TECHNOLOGY

Master of Science in Engineering Systems

and

Master of Business Administration

in conjunction with the Leaders for Global Operations Program at the

MASSACHUSETTS INSTITUTE OF TECHNOLOGY

**ARCHIVES**

JUN 28 2016

June 2016

© Naomi Arnold, MMXVI. All rights reserved.

The author hereby grants to MIT permission to reproduce and to distribute publicly paper and electronic copies of this thesis document in whole or in part in any medium now known or hereafter created.

| ${\rm Author} \ldots \ldots$ | Signature redacted                                                                                     |

|------------------------------|--------------------------------------------------------------------------------------------------------|

|                              | e for Data, Systems, and Society and the MIT Sloan School of Management<br>May 9, 2016                 |

| Certified by                 | Signature redacted                                                                                     |

| Professo                     | or of Statistics and Management Science, MIT Sloan School of Management                                |

| Certified by                 | Signature redacted                                                                                     |

|                              | Duane Boning, Thesis Supervisor of Electrical Engineering and Computer Science, MIT Department of EECS |

| Approved by                  | Signature redacted                                                                                     |

| v                            | Maura Herson<br>Director, MBA Program, MIT Sloan School of Management                                  |

| Approved by                  | Signature redacted                                                                                     |

|                              | John N. Tsitsiklis                                                                                     |

| C                            | Starence J. Lebel Professor of Electrical Engineering, IDSS Graduate Officer                           |

THIS PAGE IS INTENTIONALLY LEFT BLANK.

#### Wafer Defect Prediction with Statistical Machine Learning

by

#### Naomi Arnold

Submitted to the Institute for Data, Systems, and Society and the MIT Sloan School of Management on May 9, 2016, in partial fulfillment of the requirements for the degrees of Master of Science in Engineering Systems

and

Master of Business Administration

#### Abstract

In the semiconductor industry where the technology continues to grow in complexity while also striving to achieve lower manufacturing costs, it is becoming increasingly important to drive cost savings by screening out defective die upstream. The primary goal of the project is to build a statistical prediction model to facilitate operational improvements across two global manufacturing locations. The scope of the project includes one high-volume product line, an off-line statistical model using historical production data, and experimentation with machine learning algorithms. The prediction model pilot demonstrates there exists a potential to improve the wafer sort process using random forest classifier on wafer and die-level datasets. Yet more development is needed to conclude final memory test defect die-level predictions are possible. Key findings include the importance of model computational performance in big data problems, necessity of a living model that stays accurate over time to meet operational needs, and an evaluation methodology based on business requirements. This project provides a case study for a high-level strategy of assessing big data and advanced analytics applications to improve semiconductor manufacturing.

Thesis Supervisor: Roy Welsch

Title: Professor of Statistics and Management Science, MIT Sloan School of Management

Thesis Supervisor: Duane Boning

Title: Professor of Electrical Engineering and Computer Science, MIT Department of EECS

|                     |                 | -                  |                   |                 |

|---------------------|-----------------|--------------------|-------------------|-----------------|

|                     |                 |                    |                   |                 |

|                     |                 |                    |                   |                 |

| The author wishes t | o acknowledge t | he Leaders for Gl  | obal Operations I | Program for its |

|                     | _               |                    | _                 | •               |

|                     | $\sup$          | port of this work. |                   |                 |

|                     | $\sup_{}$       | port of this work. |                   |                 |

|                     | sup             | port of this work. |                   |                 |

|                     | sup             | port of this work. |                   |                 |

|                     | sup             | port of this work. |                   |                 |

|                     | sup             | port of this work. |                   |                 |

### Acknowledgments

This thesis would not have been possible without the help and support of many people. First I would like to thank my SanDisk supervisor, Yew Wee Cheong, for his unwavering dedication and championing of this project. A big thank you to Cindy You for her countless hours helping me - more than my "buddy" she was my confidente and friend. Thanks to the Quality Engineering team, Wenting Zhang and Xiaoqian Wang, for making me feel like part of the team.

I am grateful to SanDisk's LGO alumni for creating this amazing opportunity to work and live in Shanghai. I look up to Manish Bhatia, Kris Wilburn, and Weng-Hong Teh as leadership role models and they have been incredible mentors for me. A special thanks to the leaders across SanDisk that supported and contributed to this project. Thank you KL Bock and Gursharan Singh for sponsoring this internship to be in Shanghai. Special thanks to Itzik Gilboa for his guidance and advocacy of my project across organizations.

I would like to extend a big thank you to the teams in Shanghai, Milpitas, and Yokkaichi. In Shanghai, thank you Lena Zhang, Feiyun Zhang, Li Deng, Robertito Piaduche, and Joseph Idquival for sharing their KGD and test program expertise with me. In the Milpitas office I appreciate all the time that Hung Nguyen, Jason Yabe, Junius Tjen, and Loc Tu spent teaching me and facilitating this project. The big data strategy and machine learning analysis would not have been possible without the guidance and collaboration of Janet George, Jin Huang, Amit Rustagi, and the rest of the Big Data team. Thank you Kikuchi-san and the Yokkaichi fab team for the valuable feedback and hospitality. Thank you SanDisk and the many amazing people not named here that I had the pleasure to meet and work with.

I am humbled by this opportunity to call Professors Roy Welsch and Duane Boning my advisors. Thank you for all the time providing me with modeling guidance, knowledgeable perspective, and visits to China and California for this project.

Lastly, I cannot thank enough my family, friends, MIT classmates, and LGO compadres that have given me everything from words and wisdom to technical assistance. Your encouragement means more to me than I can express in words. I feel grateful every day to have such wonderful people in my life.

# Contents

| 1 | Intr | oducti  | ion                                                    | 11     |

|---|------|---------|--------------------------------------------------------|--------|

|   | 1.1  | Projec  | et Motivation                                          | <br>11 |

|   | 1.2  | Projec  | ct Statement and Hypothesis                            | <br>12 |

|   | 1.3  | Thesis  | s Overview                                             | <br>13 |

| 2 | Bac  | kgrour  | nd                                                     | 15     |

|   | 2.1  | Flash   | Memory Industry                                        | <br>15 |

|   | 2.2  | SanDi   | $\operatorname{sk}$                                    | <br>17 |

|   | 2.3  | Semico  | onductor Manufacturing Overview                        | <br>19 |

|   | 2.4  | Backg   | ground Summary                                         | <br>22 |

| 3 | Lite | erature | e Review                                               | 23     |

|   | 3.1  | Machi   | ine Learning Approaches to Semiconductor Manufacturing | <br>23 |

|   | 3.2  | Big Da  | ata Opportunities in Manufacturing                     | <br>29 |

|   | 3.3  | Litera  | ture Review Summary                                    | <br>32 |

| 4 | Cur  | rent P  | Process                                                | 33     |

|   | 4.1  | Manuf   | facturing Process and Test Flows                       | <br>33 |

|   |      | 4.1.1   | Wafer Fabrication                                      | <br>34 |

|   |      | 4.1.2   | Cherry Pick Wafer Sort                                 | <br>34 |

|   |      | 4.1.3   | Known Good Die Test                                    | <br>35 |

|   |      | 4.1.4   | Assembly                                               | 35     |

|   |      | 415     |                                                        | 36     |

|   | 4.2  | Descri  | iption of Data Sources                                      | 36 |

|---|------|---------|-------------------------------------------------------------|----|

|   |      | 4.2.1   | Die Sort Data                                               | 37 |

|   |      | 4.2.2   | Known Good Die Data                                         | 37 |

|   |      | 4.2.3   | Memory Test Data                                            | 38 |

| 5 | Mo   | del De  | evelopment and Results                                      | 39 |

|   | 5.1  | Model   | Preparation                                                 | 39 |

|   |      | 5.1.1   | Data Refining Approach                                      | 40 |

|   |      | 5.1.2   | Evaluation Metrics                                          | 42 |

|   | 5.2  | Wafer   | -level KGD prediction model                                 | 46 |

|   | 5.3  | Die-le  | vel KGD prediction model                                    | 49 |

|   | 5.4  | Die-le  | vel memory test prediction model                            | 52 |

|   | 5.5  | Result  | ts Summary                                                  | 58 |

| 6 | Rec  | omme    | ndations and Implementation Plan                            | 59 |

|   | 6.1  | Model   | ling Recommendations                                        | 59 |

|   | 6.2  | Cherry  | y Pick program                                              | 62 |

|   | 6.3  | Wafer   | fab                                                         | 66 |

| 7 | Stra | ategy f | or Applying Big Data and Advanced Analytics to Semiconducto | r  |

|   | Ma   | nufact  | uring                                                       | 69 |

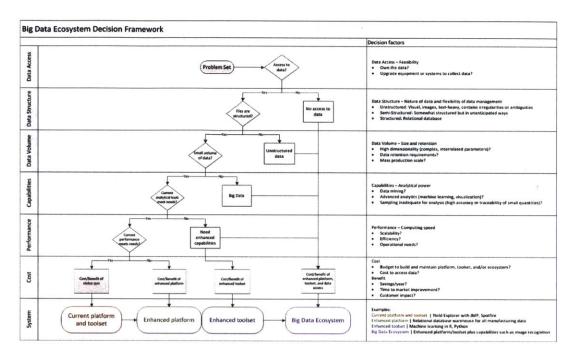

|   | 7.1  | Frame   | ework to Evaluate Applicable Problem Sets                   | 70 |

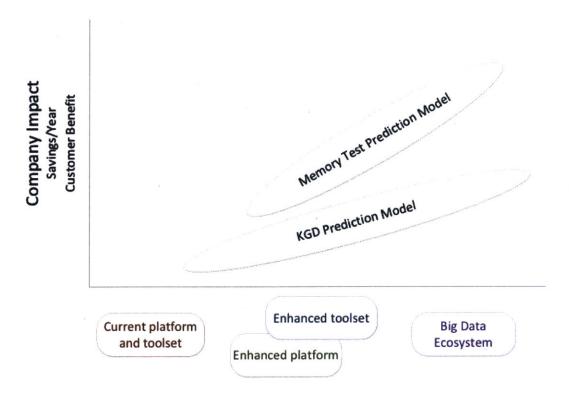

|   | 7.2  | Impac   | et Assessment Methodology                                   | 72 |

| 8 | Cor  | nclusio | $\mathbf{n}$                                                | 75 |

|   | 8.1  | Result  | ts and Limitations of Model                                 | 76 |

|   | 8.2  | Recon   | nmendations for Next Steps for Model                        | 77 |

|   |      | 8.2.1   | Enhance Model Data Sources and Logic                        | 77 |

|   |      | 8.2.2   | Simulation of Operational Model over Time                   | 78 |

|   |      | 823     | Ontimize Related Sub-processes                              | 70 |

# List of Figures

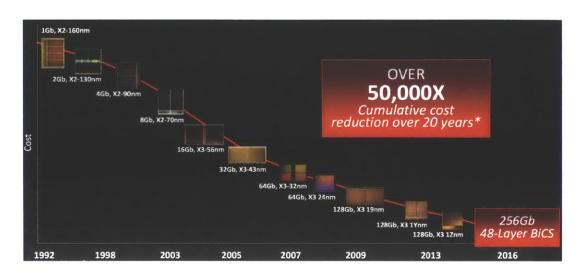

| 2-1  | Flash memory development has outpaced Moore's Law [6]                      | 16 |

|------|----------------------------------------------------------------------------|----|

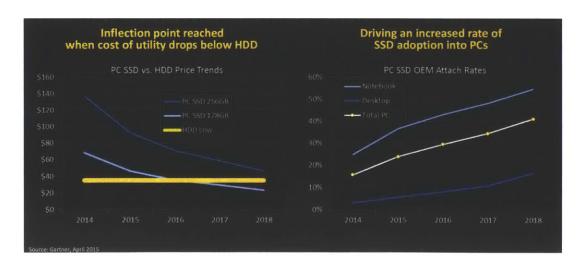

| 2-2  | Flash versus HDD price trends and PC SSD adoption [6]                      | 16 |

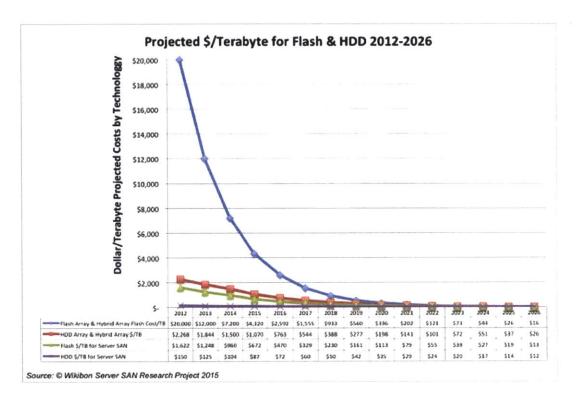

| 2-3  | Enterprise flash vs HDD cost projections 2012-2026 [32]                    | 17 |

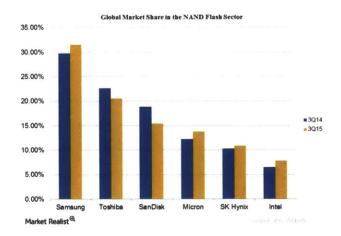

| 2-4  | Companies with largest global market share in NAND flash market, 2015 [19] | 18 |

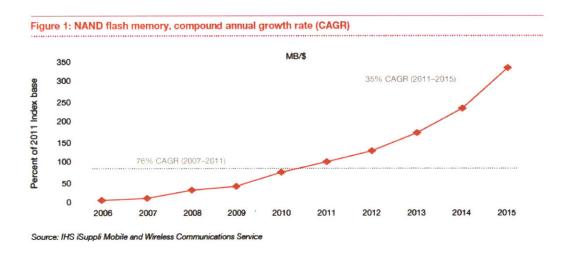

| 2-5  | Forecasted NAND flash memory market CAGR [5]                               | 18 |

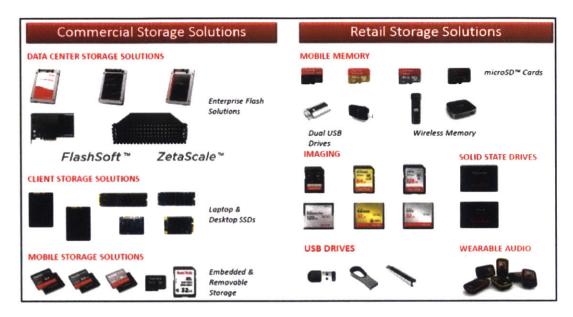

| 2-6  | SanDisk commercial and retail storage solutions [22]                       | 19 |

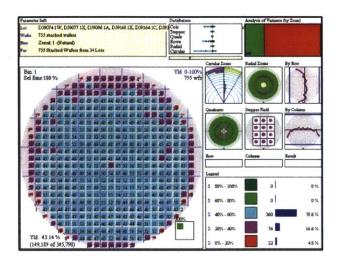

| 2-7  | Example stacked wafer map [15]                                             | 21 |

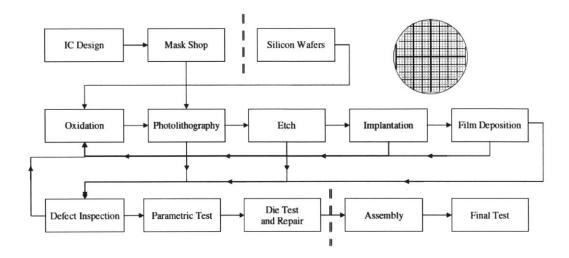

| 2-8  | High level semiconductor manufacturing process [7]                         | 22 |

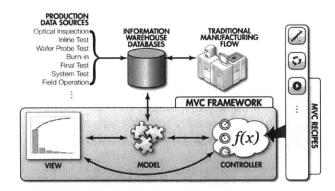

| 3-1  | High level strategy for model-view-controller architecture [14]            | 24 |

| 3-2  | Experimental approach for ML model development [14]                        | 24 |

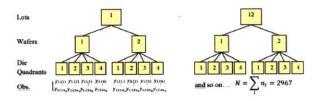

| 3-3  | Aggregated data example per die [13]                                       | 25 |

| 3-4  | Nested structure for die within wafer and lot [13]                         | 25 |

| 3-5  | Wafer map to defect bin approach [25]                                      | 26 |

| 3-6  | Data size and model run time experimental study [25]                       | 26 |

| 3-7  | Comparison of algorithms and predicted defects [18]                        | 29 |

| 3-8  | Big data ecosystem proposal [17]                                           | 29 |

| 3-9  | IBM architecture for big data analytics to cognitive computing [8]         | 31 |

| 3-10 | Case study for IBM wafer pattern detection solution [8]                    | 31 |

| 4-1  | High level overview of relevant process steps                              | 34 |

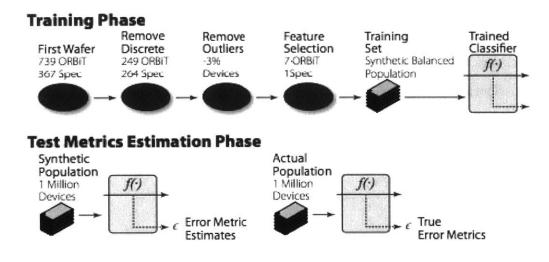

| 5-1  | Summary of model approach phases                                           | 40 |

| 5-2  | Example confusion matrix                                                   | 42 |

| 5-3  | Example receiver operating characteristic (ROC) in R                            | 43 |

|------|---------------------------------------------------------------------------------|----|

| 5-4  | Example variable importance plot from random forest output                      | 45 |

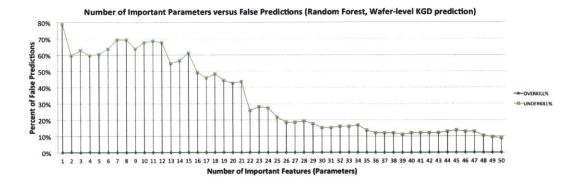

| 5-5  | Number of important features vs prediction error in wafer-level random forest   |    |

|      | prediction model                                                                | 46 |

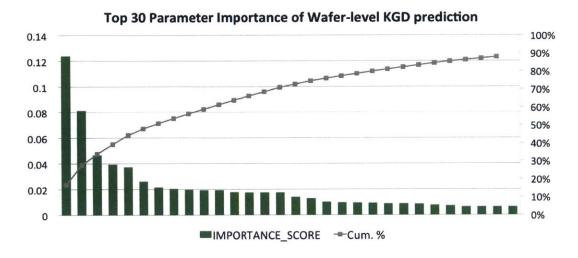

| 5-6  | Top thirty important features in the wafer-level random forest prediction model | 47 |

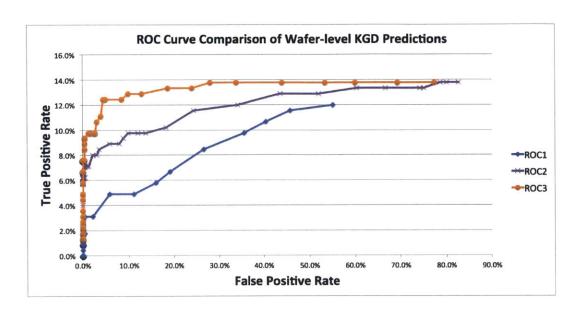

| 5-7  | ROC curves of three trials of increasing data set size                          | 48 |

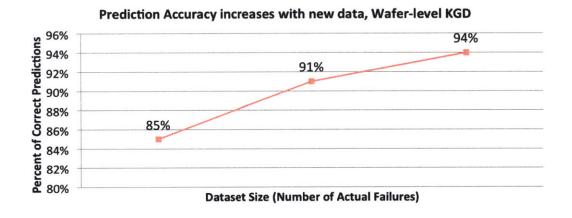

| 5-8  | Effect of increased number of failure samples in training set                   | 48 |

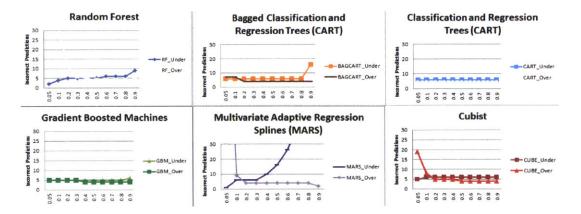

| 5-9  | Comparison of the best algorithms by threshold vs incorrect predictions         | 50 |

| 5-10 | Comparison of the worst algorithms by threshold vs incorrect predictions        | 50 |

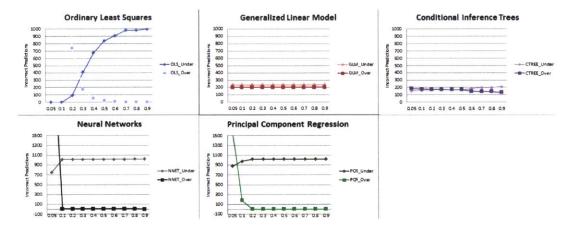

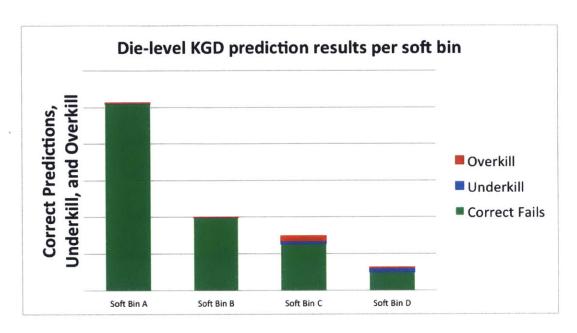

| 5-11 | Top four KGD soft bin prediction accuracy                                       | 51 |

| 5-12 | Die-level random forest KGD prediction results                                  | 52 |

| 5-13 | MT model development assumptions and data insights approach                     | 54 |

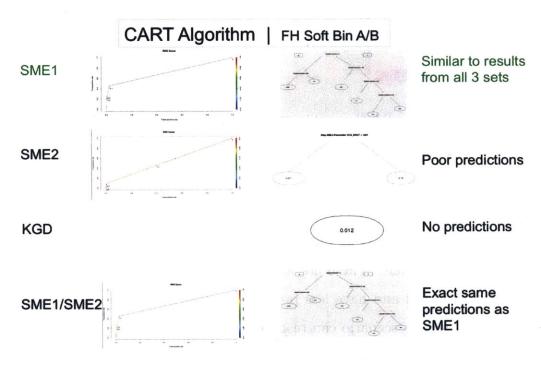

| 5-14 | Comparison of data sets and important parameters using a CART algorithm         | 55 |

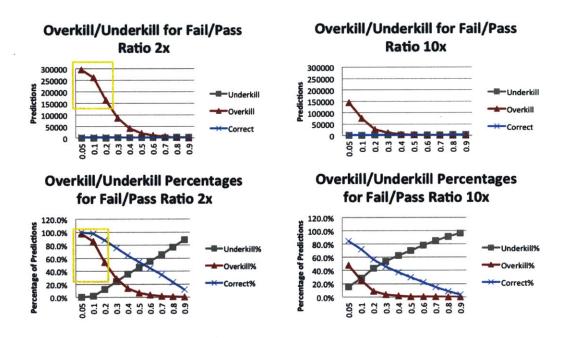

| 5-15 | Impact of sampling training set pass records                                    | 55 |

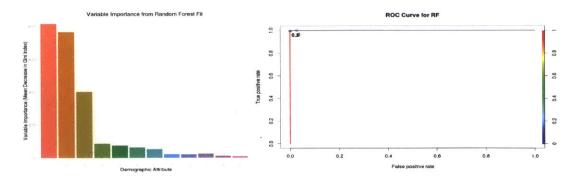

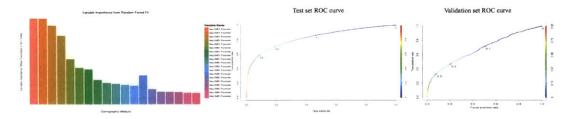

| 5-16 | Best test and validation set results from MT random forest model, variable      |    |

|      | importance plot and ROC curves                                                  | 56 |

| 5-17 | Best test and validation set results from MT random forest model, confusion     |    |

|      | matrices                                                                        | 57 |

| 5-18 | MT predictions validation results using CART algorithm                          | 58 |

| 6-1  | Prediction results incorporated into decision-making process                    | 63 |

| 6-2  | Mockup of updated wafer map based on prediction model results                   | 65 |

| J-Zi | mockup of updated water map based on prediction model results                   | υü |

| 7-1  | Decision framework for evaluating big data ecosystem opportunities              | 71 |

| 7-2  | Framework to map problem sets to opportunities                                  | 73 |

# Chapter 1

### Introduction

This chapter covers a general overview and context to introduce this project and thesis content. Section 1.1 covers the semiconductor manufacturing process context and Section 1.2 reviews how this project addresses a main challenge within this process. Section 1.3 previews the project approach and structure of this thesis.

### 1.1 Project Motivation

In the semiconductor industry where the technology continues to grow in complexity and Moore's law simultaneously drives decreases in manufacturing costs, it is increasingly important to identify defective die earlier in the process to recognize significant cost savings [10]. SanDisk would like to predict defective wafer die before two in-line test steps occur at their Shanghai assembly facility (SDSS). At the SDSS facility, wafers arrive from the wafer fabrication facility (fab) and a "cherry pick" wafer sort step identifies wafers that will meet subsequent stratified performance criteria. Then a costly test process occurs, called known good die (KGD) testing. Die are binned by KGD test results into different quality tiers and assembled into final products. After assembly, the final memory test (MT) exposes additional defects.

The KGD and MT test processes require expensive test machines, long test times, and are a reactive quality control process. Thus, there exists an opportunity for wafers with a high proportion of defects to miss KGD testing and be automatically downgraded, saving

valuable test time. There also exists an opportunity to avoid value-added assembly work for die destined to fail memory test. Multiple die (two, four, eight, sixteen, etc.) are stacked on top of each other to create one final package. Die stacking multiplies the cost implications that each defective die has on the value of the final package.

### 1.2 Project Statement and Hypothesis

The primary goal of the project is to build a statistical prediction model to facilitate operational improvements across two global manufacturing locations. A prediction model could improve the accuracy of wafer and die sorting, resulting in decreased assembly costs. It could also enable coordination with the wafer fab to implement root cause fixes to further drive cost savings. The main objective is to experiment with statistical prediction models to identify key values and correlation between die sort quality data (originating at the wafer fab) and test result data (KGD and MT that originate at SDSS). A second objective is to provide recommendations as to how a prediction model can be implemented in production to increase test yields and decrease operational costs at SDSS and at the wafer fab. Lastly, a third goal is to use this model as a case study to develop a high-level strategy for applying big data and advanced analytics techniques to semiconductor manufacturing.

Predicting defective wafer die has several major challenges. The datasets generated at the wafer fab and assembly facilities are compromised of hundreds of input variables. Mass production volumes are on the scale of millions of die each day. Thus, more resources are required to analyze this "big data" problem set. Existing analytical methods are not accurate enough for predictions since prior quality analyses are usually based on sampling. Another challenge exists due to the nature of the problem spanning multiple manufacturing locations. Access to data and coordination between international facilities are longstanding issues. As a result, SDSS lacks insight into the meaning of the fab's die sort parameter data and the upcoming, continual changes in processing at the fab. Currently, the KGD test process applies program-specific tests in place of full insight into and control over the fab die sort test results.

The project's main hypotheses are to predict a binary outcome of the known good die

defect category ("KGD soft bin") and memory test defect category ("test block number" or "FH soft bin"). The KGD prediction uses the primary upstream fab die sort (DS) test result data (called SME1). The memory test prediction model uses SME1 data and two additional upstream data sets as inputs (fab low temperature test result data, SME2, and known good die test parameter results). Input data sets are explained in more detail in Chapter 5. The project aims to build two prediction models that can identify die defect categories to an acceptable accuracy level that would meet business requirements. If the hypothesis can be proven, then implementation of the prediction model would result in wafers skipping KGD testing and avoidance of memory test failures. A small yield improvement of the KGD or MT test would result in significant financial savings given the high production volumes.

#### 1.3 Thesis Overview

The thesis is laid out in seven main chapters. Chapter 2 gives context on the industry, San-Disk as a company, and high-level overview of the semiconductor manufacturing process. In Chapter 3, relevant academic and industry publications are analyzed that provide examples of other machine learning methodologies in semiconductor manufacturing along with background in yield modeling and big data applications. Chapter 4 explains the manufacturing flow, starting from the fab to the final testing at the assembly facility, in order to provide context as to how a prediction model would fit into this process. Chapter 5 provides the details of the model development process and results of three prediction models. In Chapter 6, recommendations present how to incorporate the prediction model into the current process. Chapter 7 proposes a strategic analysis of how to assess big data and advanced analytics opportunities in a semiconductor manufacturing environment. Lastly, Chapter 8 summarizes the main findings and next steps to improve and expand the prediction model.

This thesis also covers analyses and assumptions about the prediction model formulations. Algorithm experimentation was included in modeling since we assume that different wafer technologies need different algorithms and tuning to optimize prediction accuracy, reviewed in Section 3.1 and tested in Section 5.3. Another hypothesis is that the prediction models require large sample size of defects. Given low defect rate, large data sets are analyzed

along with various sampling methods in Section 5.4. Another hypothesis is that the models need to be updated in an intelligent manner to remain accurate over time, due to constant wafer fabrication facility process changes. Thus, experimentation with date ranges in the training and testing data sets are included in Section 5.4. Another area of exploration was the computational performance of the hardware that could handle this size of data set. R Studio is utilized in an off-line model on external servers with in-memory processing. Many other platforms and tools exist; alternative options are detailed in Section 3.2.

# Chapter 2

# Background

Chapter 2 covers background on the flash memory industry, SanDisk company history, and a high level overview of semiconductor manufacturing. Section 2.1 provides a context on technology development according to Moore's law, the competitive landscape, and industry growth. Section 2.2 includes basic facts about SanDisk as a company, its line of products, and current manufacturing locations. Section 2.3 discusses the main process steps for any semiconductor manufacturer, how to calculate test yields, and failure modes.

### 2.1 Flash Memory Industry

SanDisk operates in the flash storage solutions market where NAND is the primary technology. NAND benefits from a small form factor, high performance write speed, and solid-state format which enables data retention without a power source (non-volatile). The flash memory market has been characterized by fast-paced technology developments that decrease the price per bit [21]. Increased density of memory die per wafer has resulted in the capacity of each chip each year to outpace Moore's Law (Figure 2-1).

NAND flash memory advantages have resulted in disruption of the storage market as seen in Figure 2-2 and 2-3. Flash memory has been adopted in a large range of devices, replacing hard disk drive (HDD) technology. Analysts project that "the rapidly lowering cost and higher performance of flash will result in a rapid adoption of flash to replace magnetic drives. Flash together with systems of intelligence will enable the integration of big-data

Figure 2-1: Flash memory development has outpaced Moore's Law [6]

Figure 2-2: Flash versus HDD price trends and PC SSD adoption [6]

Figure 2-3: Enterprise flash vs HDD cost projections 2012-2026 [32]

analysis into operational systems, and automate many decisions" [32].

The flash memory space is highly competitive. The main players include SanDisk, Samsung, Toshiba, Micron, Hynix, and Intel. Market share from Q3 2014 and 2015 are shown in Figure 2-4 [19].

In PricewaterhouseCooper's mobile technologies index, the compound annual growth rate for NAND flash memory was estimated to be 35 percent between 2011-2015, measured in megabytes per dollar as seen in Figure 2-5. The slim form factor of the solid state drive (SSD), which uses NAND as the storage component, will soon be the standard for tablets and smartphones. With the drop in price, original equipment manufacturers (OEMs) are turning to SSDs for desktops, laptops, and servers for price-performance advantages [5].

### 2.2 SanDisk

SanDisk is the worlds largest pure play supplier of flash memory data storage products. SanDisk was founded in 1988 by Eli Harari, Sanjay Mehrotra and Jack Yuan. Its stock,

Figure 2-4: Companies with largest global market share in NAND flash market, 2015 [19]

Figure 2-5: Forecasted NAND flash memory market CAGR [5]

SNDK, began publicly trading on NASDAQ in 1995. SanDisk is a US Fortune 500 company. In the past ten years, over one billion SanDisk memory cards were sold. SanDisk's mission is "to enrich people's lives through digital storage anytime, anywhere" and the company has about 8,600 regular employees. Products include flash storage solutions for enterprise data centers and client computing platforms (SSDs), removable and embedded flash products (mobile phones, cameras, automotive, connected home electronics, USB flash drives, DRAM, digital audio players, and SIM cards). Most products combine NAND flash memory with a controller and firmware, mostly designed in-house [21].

In 2014, SanDisk had revenues of 6.1B USD with commercial products (OEM's) accounting for two thirds and one third from retail products. Net cash in 2014 was 1.9B USD and

Figure 2-6: SanDisk commercial and retail storage solutions [22]

the company spent 0.9B USD on research and development investment that year. In October 2015, SanDisk announced that it will be acquired by Western Digital Corp. in a 19B USD deal [1].

SanDisk manufacturing facilities are located in China, Japan, and Malaysia. SanDisk Shanghai (SDSS) opened in 2006 and the facility covers assembly, test, packaging, and distribution of advanced flash memory products. SanDisk and Toshiba have a joint venture of the wafer fabrication facility in Yokkaichi, Japan. In 2002, SanDisk and Toshiba moved all of their NAND flash wafer production to the fabs in Yokkaichi. SanDisk has twenty global locations and is headquartered in Milpitas, California [23].

### 2.3 Semiconductor Manufacturing Overview

Semiconductor manufacturing is the process of taking a silicon wafer and adding layers that are patterned into integrated circuits (IC's). These are diced into individual die and packaged to be used in digital devices. This complex manufacturing process includes hundreds of steps.

Physical defects and variation that occur during manufacturing cause individual die and packages to fail to perform as desired. There are different categories of failures that affect semiconductor manufacturing yields. Parametric failures result from control deviations and

are associated with quality losses or functional failures. Area dependent failures occur on certain areas, such as foreign particles landing on the wafer. Random failures are uncorrelated and occur spontaneously. Generally, discrete failure probabilities are not Gaussian. They can be spatial in nature or based in binomial and Poisson statistics. Area dependent failures such as foreign particles cause different types of issues, such as distorted pattern layers, mechanical stress within the circuit if trapped between layers, or electrical shorts or opens. Non-local defects can also exist and are usually spatially correlated so they result in a clear spatial pattern; these may be caused by process variation [2].

The volume of die that perform as desired divided by the total number of die manufactured at that step is called the yield [7] and is usually reported as a percentage.

$$Yield = \frac{Good}{Total}\%$$

Yield can be calculated for each manufacturing test step and overall yield is the product of each of the steps.

$$Yield_{Total} = Yield_1 * Yield_2 * ... Yield_N$$

Assuming that a die will not perform as desired unless it is free of defects, the probability that a die successfully performs equals the probability that no defects exist on its area. Larger die area results in higher odds that it can include one or more defects. Wafers with large printed die have a lower die yield than small die wafers, even if they are developed by the same fabrication process and have the same defect density. Die yield losses from mis-processing can also escape detection in-line and during the parametric test. Some kinds of mis-processing impacts only a portion or die per wafer, for example edge loss due to less controlled film deposits near the edge of the wafer. A wafer map visualizes die yield by position on the wafer. As seen in Figure 2-8, an example stacked wafer map displays the average yield by die position [15].

Integrated circuit design results in a reference of electrical and physical characteristics of a complex electrical circuit device that uses semiconducting materials. A complete IC can contain millions of simple devices (resistors, transistors, diodes, capacitors) that work

Figure 2-7: Example stacked wafer map [15]

together to perform functions such as memory or microprocessor. These IC designs are converted into layers that create electrical circuits when vertically integrated. The mask shop uses the design as an input to create a mask for each layer with geometric patterns. During wafer fabrication, many layers on each wafer are processed and each area of a single completed IC is called a die.

The wafers are made from silicon, which are grown from single crystals into silicon ingots. These ingots are sliced and polished, resulting in individual wafers. The wafer fab then performs hundreds of processing steps on the wafers. Wafers are oxidized by heating the wafers to a high temperature in an oxygen rich environment. Film deposition adds a layer of material on top of the wafer that is either conductive or non-conductive. Photolithography creates the pattern on the layer by applying photoresist, exposing the mask's circuit pattern, and developing the photoresist. Etch removes non-patterned surface layer or layers after photolithography. The photoresist is removed, leaving the patterned film on the wafer. In implantation, the wafer is doped with active ions to modify the properties of the wafer material as desired.

Each die on the wafer is probed, tested, and sorted so that bad dies are identified. Examples of testing include input and output voltages, current, signal timing, operational logic, and frequency of operation. "Bad" die fall into different failure categories ("binning") that assign a unique code. Hard bin refers to an overall pass or fail. Soft bin refers to a

Figure 2-8: High level semiconductor manufacturing process [7]

categorization of failure, defined by test engineering. The yield is calculated at the end of this step.

The next main process is assembly. During assembly, wafers are transformed into individually packaged IC's. The wafer is cut (singulated) along scribe lines to separate each die. Each die, or stack of multiple die, is encapsulated in a package and metal connections are made. Packages can also be called chips or units. At the end assembly and packaging, final test occurs to ensure that the package passes electrical and environment requirements and final yield is calculated. Final test is the measure of the entire package's performance and meant to simulate extreme conditions of the real world [7].

### 2.4 Background Summary

SanDisk operates in a highly competitive, rapidly evolving flash memory industry. The flash memory manufacturing process is complex and capital intensive. SanDisk aims to gain competitive advantage in this space via technological innovation and streamlined operations. Chapter 3 will overview new areas of research in applying machine learning and big data to semiconductor manufacturing at other academic institutions and industry players. The new analytical capabilities provided by big data platforms, widely utilized in other technology and internet companies, can enhance current statistical quality control procedures at SanDisk.

# Chapter 3

### Literature Review

This chapter covers relevant industry and academic research in the areas of machine learning approaches in Section 3.1 and big data applications to semiconductor manufacturing in Section 3.2. Ideas from these references support and inspire the formulation of the prediction model methodologies discussed in Chapter 5. Section 3.3 summarizes the main takeaways from the literature review process.

# 3.1 Machine Learning Approaches to Semiconductor Manufacturing

A high level overview of the impact of applying machine learning to other manufacturing improvements is explored by Susto et al., covering virtual metrology, predictive maintenance, fault detection, run-to-run control, and modeling [26]. Challenges are outlined such as high dimensionality data, data fragmentation, time series input data, and multi process modeling. Many of these issues are encountered in our problem, as will be discussed in Chapter 5. Dimensionality reduction techniques are proposed by Susto et al. (principal components and correlation analysis, stepwise selection) to address the first challenge. Other ideas are proposed to help tackle the other challenges (data clustering and supervised aggregative feature extraction), yet validation and customization is found to still be needed on a case by case basis [26].

Figure 3-1: High level strategy for model-view-controller architecture [14]

Fig. 7. Summary of experimental approach

Figure 3-2: Experimental approach for ML model development [14]

A TI/IBM case study by Kupp and Makris argues that studying data together from manufacturing and test flow is necessary to find process variability, since isolated statistical data analysis misses intra-process and test correlations [14]. The authors find that testing can account for up to 50 percent of the overall cost of an integrated circuit. Reducing test cost can be addressed by developing algorithms for post-production performance and spatial modeling of sparsely sampled wafer test results. The paper proposes a model-view-controller architecture for rapid iteration of complex machine learning methods to find optimal solutions with large datasets. The proposed framework and analysis methodologies are pictured in Figs. 3-1 and 3-2 [14].

| LotID | WaferID | DieX | DieY | Defects<br>on Layer<br>1 | Defects<br>on Layer<br>2 | Bin | Fail = 1 |

|-------|---------|------|------|--------------------------|--------------------------|-----|----------|

| 1     | 2       | 1    | 9    | 0                        | 2                        | 1   | 0        |

| 1     | 2       | 2    | 7    | 1                        | 0                        | 1   | 0        |

| 1     | 2       | 3    | 12   | 0                        | 1                        | 1   | 0        |

| 1     | 2       | 4    | 3    | 1                        | 0                        | 1   | 0        |

| 1     | 2       | 4    | 15   | 0                        | 1                        | 1   | 0        |

| 1     | 2       | 5    | 6    | 0                        | 1                        | 1   | 0        |

| 1     | 2       | 5    | 7    | 1                        | 0                        | 1   | 0        |

| 1     | 2       | 5    | 8    | 0                        | 1                        | 1   | 0        |

| 1     | 2       | 5    | 10   | 0                        | 1                        | 42  | 1        |

| 1     | 2       | 5    | 11   | 1                        | 0                        | 1   | 0        |

| 1     | 2       | 5    | 15   | 1                        | 0                        | 1   | 0        |

| 1     | 2       | 6    | 15   | 1                        | 0                        | 1   | 0        |

| 1     | 2       | 7    | 3    | 1                        | 0                        | 1   | 0        |

| 1     | 2       | 7    | 11   | 0                        | 1                        | 1   | 0        |

| 1     | 2       | 7    | 15   | 1                        | 0                        | 1   | 0        |

| 1     | 2       | 8    | 8    | 1                        | 0                        | 24  | 1        |

| 1     | 2       | 8    | 16   | 1                        | 0                        | 1   | 0        |

| 1     | 2       | 9    | 1    | 1                        | 3                        | 7   | 1        |

| 1     | 2       | 10   | 1    | 0                        | 1                        | 77  | 1        |

| 1     | 2       | 11   | 1    | 0                        | 2                        | 1   | 0        |

| 1     | 2       | 11   | 17   | 1                        | 1                        | 1   | 0        |

| 1     | 2       | 13   | 16   | 1                        | 1                        | 1   | 0        |

| 1     | 2.      | 18   | 8    | 1                        | 1                        | 1   | 0        |

| 1     | 2       | 18   | 9    | 1                        | 1                        | 7   | 1        |

| 1     | 2       | 18   | 10   | 1                        | 1                        | 1   | 0        |

Figure 3-3: Aggregated data example per die [13]

Figure 3-4: Nested structure for die within wafer and lot [13]

Krueger considers semiconductor yield modeling using generalized linear models, and provides valuable reference information for detailed approach methodology and data analysis [13]. The main strategy proposed to forecast yield is generalized linear models (GLMs) using defect metrology data. The research also integrates classification and regression trees (CART) with GLMs. The approach spans wafer-level and die-level analysis, and finds dielevel predictions to be more accurate than wafer-level data sets, and that these performed better with larger sample sizes. The research shows that GLM models provide better predictions than the best historical model (Seeds Yield Model, an existing equation to predict performance based on defect count data). Krueger uses raw data structured in a similar manner as our data (described in Section 4.2), as pictured in Figure 3-3. The strategy of nesting die within wafers and lots as used by Krueger (Figure 3-4) is considered as a potential next step in our work in Chapter 8 [13].

Figure 3-5: Wafer map to defect bin approach [25]

TABLE 1.1. Number of Points and Their Corresponding Run Time

| Number of Points | Run Time (seconds) |

|------------------|--------------------|

| 325 (5%)         | 2,395.44           |

| 649 (10%)        | 12,453.28          |

| 974 (15%)        | 24,922,63          |

| 1,298 (20%)      | 51,112.13          |

| 1,623 (25%)      | N.A. <sup>a</sup>  |

| 1,947 (30%)      | N.A.               |

| 2,272 (35%)      | N.A.               |

| 2,596 (40%)      | N.A.               |

<sup>4</sup> N.A., not available.

Figure 3-6: Data size and model run time experimental study [25]

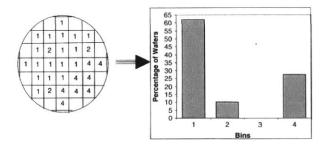

A methodology for defining the top defect bins to target is outlined by Soenjaya et al. [25]. The wafer map to defect bin approach (Figure 3-5) shows an example of a wafer that has 29 dies and four bins. Also pictured are the results from this experimental study's run time analysis, in Figure 3-6. The impact of increasing data size (2.5GB after data processing was complete) is seen to adversely affect run time. This analysis was performed using four months of STMicroelectronics wafer fabrication data on a Unix server Sunfire with algorithms implemented in Java [25].

Several publications describe successful experiments using a variety of machine learning algorithms. Support vector regression is successfully used by Lenz and Barak to improve virtual metrology [16]. They also note that approximately 50 percent of the time on the project was invested in data preparation. The authors state that simple and multiple linear

regression is not suitable for virtual metrology due to lack of accuracy and robustness. In their approach, predictive power is evaluated by the coefficient of determination (R) and accuracy is measured with mean square error (MSE), root-MSE (RMSE) and coefficient of variation. In terms of addressing outliers, their approach elects to not remove them, since it is assumed that important characteristics would be removed as well. This research had access to six months of process and metrology data, and found that only 1.6 percent of the original data set was suitable for analysis once wafers with missing data were removed. The authors also use expert input to identify the top six parameters and to decrease input parameter data set size before modeling. Results show R = .64 and CV(RMSE) = 1 percent, demonstrating the high predictive power of support vector regression in this problem [16].

Rosa and Vladimirov use another algorithm methodology, support vector machines (SVM), to improve quality control by early prediction of manufacturing outcomes [20]. In this approach, SVM with non-linear kernels on a per chip model tends to perform better, but not well enough to implement in production effectively. The authors did find that applying the SVM model to wafer-level classification results in the prediction accuracy for low-yield wafers to be as high as 81 percent. This paper highlights the potential advantages of wafer-level classification over die-level modeling [20].

Weiss, Dhurandhar, et al. use IBM data to discover that an ensemble method with boosted trees and linear regression to be the best performing machine learning algorithm [30]. The authors designate a proxy for microprocessor chip speed as the predicted outcome. 125 wafers (5 lots) are in the data set and data is sampled at 10 percent. Their approach also fills in missing values with a feature mean. The model data inputs are wafer control measurements, such as lithographic metrology and electrical measurements. Similar to Lenz and Barak, 90 percent of the data is missing since it was based on measurements. The analysis finds that independent time-ordered sets are advantageous over randomly sampled wafers or lots since results change over time and the population is not stationary. The authors recommend using a large test set that spans a long time frame, representing varying conditions and recent data for the training set. The authors show that the classical linear model usually performs worse than forests, but the authors hypothesize that in non-stationary environments, such as fab performance evolving over time, the linear method could win since

it tends to not over fit the data. The authors propose averaging the two methods of forests and linear regression. Similar to the results discussed in Chapter 5, this paper lists the technical difficulties of predicting time-varying populations and missing data. To address this challenge, the authors propose incremental updates to the models as new measurements are recorded. This methodology requires specialized algorithms to add new wafers and keep older wafers with additional information and knowledge of chip-making to create a new class of methods to predict chip performance over time [30].

Two other publications explore neural networks as potential algorithms. Wu, Zhang, et al. demonstrate a fuzzy neural network approach for die yield prediction can achieve better precision than the Poisson, negative binomial, and neural network models [33]. In Hsu and Chien, a hybrid data mining approach for pattern extraction from wafer bin maps explores clustering and neural network models to improve yields at a wafer fab in Taiwan [9]. These authors focus on spatial statistics to extract patterns associated with manufacturing defects but note that further research is needed to develop different methodologies to identify specific patterns [9].

A recent publication by Kang, Cho, et al. demonstrates that wafer map spatial factors have the ability to predict die-level failures in final test [12]. The model inputs are four derived variables pertaining to wafer map features. The model predicts two types of failures using random forest algorithm. The authors demonstrate that variables based on die position are relatively more important and that prediction performance may decrease over time. The authors propose that including data from assembly, wafer fab, and test will enrich the parameter data set. Chapter 8 recommends a similar next step for this analysis since spatial factors appear to be very important in final test prediction modeling [12].

Another publication by S. Park, C. Park, et al. finds a similar result about the importance of spatial factors for pattern recognition using feature based die-map clustering [18]. In this approach, different response variables are tested (A: column fail bit count (FBC), B: column and row FBC, C: detailed column and row FBC) by three different algorithms, pictured in Figure 3-7. Fail and Pass Classification Accuracy FCA, PCA) are the designated evaluation metrics. The authors state that big data analysis is essential for this study and propose feature extraction from FBC data [18].

| Model          |     | Type A | Type B | Type C |

|----------------|-----|--------|--------|--------|

| D 11 - T       | FCA | 0.8225 | 0.7830 | 0.8354 |

| Decision Tree  | PCA | 0.7972 | 0.8069 | 0.8352 |

| Support Vector | FCA | 0.8635 | 0.6084 | 0.9489 |

| Machine        | PCA | 0.8795 | 0.6934 | 0.9619 |

| Artificial     | FCA | 0.4382 | 0.7478 | 0.9461 |

| Neural Network | PCA | 0.7391 | 0.3785 | 0.2885 |

Figure 3-7: Comparison of algorithms and predicted defects [18]

### 3.2 Big Data Opportunities in Manufacturing

The following section provides references to recent publications exploring big data and its applications in manufacturing. Some publications are high level strategic architectures and others are research based, using fab data for empirical studies or simulation.

What is big data? Big data is the convergence of internet, business, and sensor data that necessitates a new generation of architectures for analysis. It is significantly larger in scale than traditional data sets and is usually measured in petabytes. Big data also usually contains high dimensionality (thousands or millions per element) and a large diversity of data (semi-structured or unstructured). The data is usually combined across multiple sources, flows at a rapid rate, and uses adaptive or machine learning-based analytics to handle the large data set size. As new hardware and software technologies arise to support the growth of big data, it is expected that opportunities for semiconductor players will be significant [10].

#### V. CONCEPTUAL BIG DATA ARCHITECTURE

Figure 3-8: Big data ecosystem proposal [17]

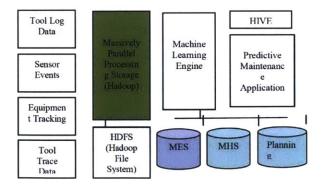

Munirathinam and Ramadoss review various big data system architecture elements, such as Hadoop, NoSQL, and Random Forest, to describe how big data predictive analytics can be applied to proactive semiconductor equipment maintenance (Figure 3-8) [17]. The authors describe the potential to move the semiconductor industry from a reactive to a predictive state in the areas of virtual metrology, predictive maintenance, fault detection, run-to-run control, and modeling. They posit that these predictive states can prevent unplanned down-time, extend the useful life of semiconductor equipment, and improve product quality [17].

Wang and Alexander provide a comprehensive overview of various manufacturing fields and processes that can benefit from big data improvements to design and operations [29]. The authors summarize the four main characteristics of big data as high volume, high velocity (collected, processed, and visualized in real time), high variety (many types of information), and high veracity (accurate and comprehensive). They also prescribe the services required to support a big data environment: cloud infrastructure (storage, compute, virtual machine management), clusters, Hadoop related services/tools, analytics tools (logs, data mining, events), databases and servers (SQL, NoSQL), massively parallel processing databases, registries, indexing/search, and security provisions. The authors describe how big data can be applied across industries since it has applications in quality, time, costs, and mass-customization. For manufacturing engineering, the authors propose that the largest impact would be on detecting defects, boosting quality, and improving supply forecasting. Design and manufacturing opportunities are prevalent in other industries such as electricity, automotive, missile, integrated circuits, semiconductors, additive manufacturing, and medical devices [29].

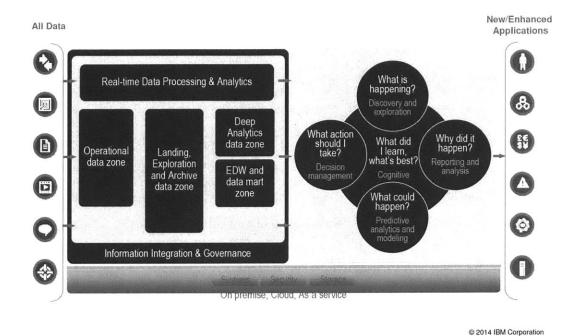

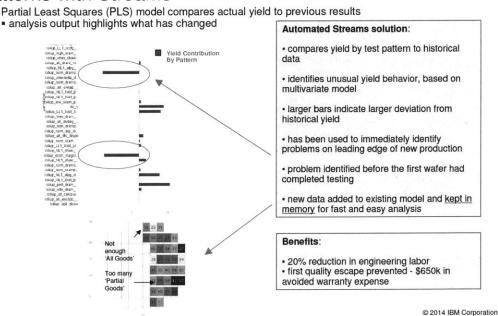

An IBM report about big data and analytics for semiconductor manufacturing show IBM's microelectronics organization successfully integrates a big data platform and custom applications in their microelectronics organization based on IBM's analytics and manufacturing expertise [8]. IBM combines data from the fab (metrology, logistics, test, sensors, inspection) to predict yield analyses and identify top variables. IBM demonstrates the automation of data analysis and multivariate analysis of wafer test patterns to detect yield changes and sensor data in IBM fab to optimize assets and yield control (Figure 3-10) [8].

Chien and Chuang propose a framework for root cause detection of sub-batch processing

Figure 3-9: IBM architecture for big data analytics to cognitive computing [8]

# Use Case 1: Real-time multivariate analysis of wafer test patterns with Streams

Figure 3-10: Case study for IBM wafer pattern detection solution [8]

system for semiconductor manufacturing big data analytics [4]. This publication finds that the primary factor to increase screening efficiency is to leverage the random forest algorithm in a sub-batch processing model that handles collinearity and dimensionality. This study validates the approach with a Taiwan fab empirical study and simulations. The authors recommend to implement these sub-batch processing systems in order to catch a small number of errors with high accuracy [4].

Tsuda, Inoue, et al. propose a similar strategy to apply big data to advanced semiconductor manufacturing using Panasonic in-line fab data [27]. Their approach incorporates a big data model with a fab-wide fault detection and classification system to stop equipment and lots automatically when a fault condition is detected. This data feed extracts equipment parameters and implements virtual metrology along with run-to-run functions that are aimed to reduce process variation [27].

### 3.3 Literature Review Summary

Based on the literature review above, several data refining methodologies are adopted in the model development discussed in Chapter 5. Similar findings about modeling challenges are described in Section 3.1 are echoed by this thesis, such as computational limitations of big data sets [25], technical difficulties of predicting time-varying populations [30], data preparation accounting for a bulk of model development time [16], and data fragmentation [26]. In terms of data refinement, methodologies are adapted in Chapter 5 based on the analysis summarized in Section 3.1, such as outlier values remaining in the input parameter data sets [16], die-level granularity for modeling [13], selecting the top defect bins for analysis [25], and experimentation with various machine learning algorithms. Other methodologies are listed as next steps to enhance the model in Chapter 8, such as including spatial input factors, nesting the die within wafers, decreasing the input parameter data set size, exploring wafer-level granularity, using the feature mean to fill in missing data fields, and enriching the parameter data set with assembly, wafer processing, and more extensive test output data sets. Section 3.1 reviews other proposals, frameworks, applicable processes, and successful case studies from other companies to support the big data strategy discussed in Chapter 7.

# Chapter 4

### Current Process

Chapter 4 provides an overview of the current state of the manufacturing and test process along with a description of the data sources utilized in the prediction model. Section 4.1 covers the main steps of the manufacturing process within the wafer fab and assembly facilities that are related to this project's problem statement. Section 4.2 reviews the die sort, known good die, and memory test data source structures to provide an understanding of the data used for modeling in Chapter 5 and to highlight potential data challenges.

### 4.1 Manufacturing Process and Test Flows

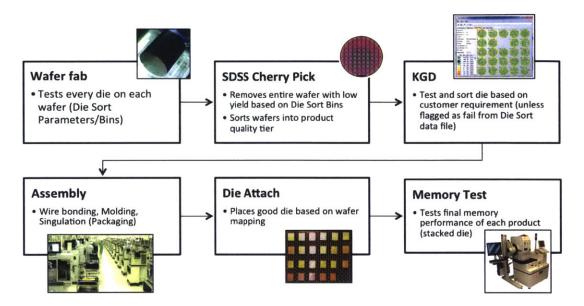

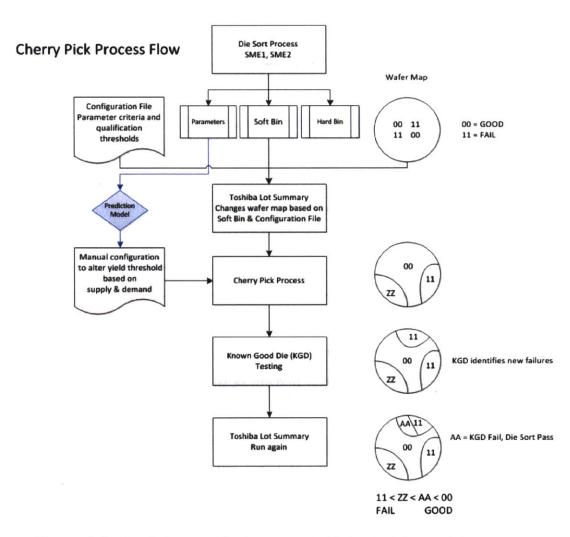

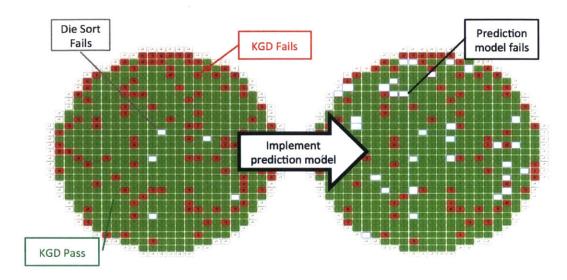

The important steps in the current manufacturing process are highlighted in Figure 4-1. Every die is tested at the wafer fabrication facility through a standard test process that generates die sort parameters and bins. The wafers are shipped to SDSS and are sorted into different expected quality tiers based on the die sort data in a process called cherry pick. Each cherry picked wafer undergoes the KGD test, which vary by customer requirements and engineering analysis. During assembly, singulated die are attached to substrates and stacked to create various products (for example, 4 stack or 8 stack die). At the end of assembly, the final products are tested thoroughly before being released to customers or downstream processing (for example, solid state drives, SSDs).

There exist additional quality procedures (in-line, statistical process control, and engineering failure analysis) but these will not be addressed in this study.

Figure 4-1: High level overview of relevant process steps

#### 4.1.1 Wafer Fabrication

Two main data sets are generated at the wafer fabrication facility. The first is called SME1 (high temperature) and the second is called SME2 (low temperature). If a die fails SME1 then it is not tested in SME2. A die must pass both tests in order to be tested in KGD.

### 4.1.2 Cherry Pick Wafer Sort

The cherry pick process is controlled by product and test engineering experts. The purpose of cherry pick wafer sort is to identify wafers with high proportion of prime die that should be assembled into products that require the highest performance levels. These wafers undergo a more stringent KGD test program, and subsequent assembly and test processing differs as well. The cherry pick process controls how wafers are sorted by increasing or decreasing yield thresholds. These alterations also create levers to incorporate wafer availability and supply and demand in the market. New criteria are continuously reviewed and tested for all production lines and initially for new products during qualification stages. Criteria are statistically analyzed by experts to filter out die that exhibit known failure modes. Criteria are based on continuous die sort parameter output values. Each cherry pick rule set varies by product configuration so there is a large quantity of KGD test versions.

Incoming wafers are stored in a wafer bank on site at SDSS and volumes are planned weekly, based on demand. Wafers can also be sold direct to some customers. The physical cherry pick process runs non-stop and typically is completely automated except in some rare cases. The machines sort wafers from their incoming jar into three assembly lot cassettes that represent different quality levels. The machines run from lot files downloaded from networked servers that contain a predetermined wafer sort allocation.

#### 4.1.3 Known Good Die Test

Upon arrival at SDSS the first test procedure, KGD, takes place before assembly processing begins in order to identify good and bad die according to customer specific requirements. Before KGD, wafers are prepared to mimic the customer placing the die on the substrate. This puts stress on the wafers so defective die can be discovered during KGD. There are hundreds of KGD tester machines that do simultaneous touch downs with two cassettes at a time. KGD testers generally run around the clock.

KGD failures are downgraded to lower performance products and KGD passes proceed to be assembled into prime products. A portion of die are skipped if they were already identified as a failure from the wafer fab die sort parameter testing. These may still be suitable for lower performance products, as a goal is to avoid wasted die wherever possible.

#### 4.1.4 Assembly

The SDSS assembly process is broken into two main categories: front end (surface mount technology to wire bonding) and back end (molding to package saw). Inputs to assembly are the wafers that passed die sort and KGD and incoming materials, such as gold wire and substrates. First, a surface mount technology step occurs which includes solder paste mounting of passive components. Then, taping and grinding of the wafer is performed to protect it during wafer thinning (die preparation). After die preparation, singulation of each die with a diamond saw occurs and die are glued to the substrate. Wire bonding attaches gold wires from the wafer to the substrate circuit. Molding encapsulates each device with mold compound. The products are given ink marks or laser markings, such as the SanDisk

or customer logo. Lastly the package saw separates each final package.

#### 4.1.5 Memory Test

At the end of processing when the products have been assembled in their final form, several tests are performed. The tests include a procedure to identify assembly-caused defects. A package preparation process occurs for certain products to stress each unit. The memory test verifies memory functionality and the factory high temperature (FH) is the most important memory test for most products. A low temperature test can also be applied for certain products. Some products are tested in both temperature levels and needs to pass both tests to be released to customers. A final test takes place which verifies the total performance of the product, called the system test. These different test programs, temperatures, and package preparation processes depend on the product design and customer requirements.

There are hundreds of memory test machines and each machine tests one lot in order to avoid mixing up the lots. The key goal of the memory test is to reduce test time since the memory test machines are the main bottleneck in the manufacturing flow, take up significant space, and are very expensive. Die can end up in nine different hard bins after memory test and some may be be re-tested due to test program issues or setting errors. Two types of testers exist (older and newer) and only data from the older testers are included in this study; products are tested randomly between tester types, so the fact that only data from the older tester version is included in the model is ignored.

### 4.2 Description of Data Sources

Test data is stored in one data repository system but requires manual extraction and merging. The following section describes the data sources involved in building the model. Die sort test data originates in the machines of the wafer fabrication facility and is processed into smaller files per lot. These files are encrypted, compressed, and transferred to the server where the data repository is located. A customized process analyzes the files for the cherry pick process and loads the data into the repository. Similarly, KGD and memory test data originates in the test machines in SDSS. These raw files are processed, aggregated, transferred, and uploaded

to the same data repository.

#### 4.2.1 Die Sort Data

Die sort parameter and die sort bin data exist in different tables within the structure of this data repository. They must be joined on lot, wafer, die x, die y coordinates as the unique key value. Die sort bin data contains a binary pass or fail attribute and one soft bin for each die. Parameter data contains each die sort parameter test name and its value. There are roughly 600+ die sort parameters in the data sets for this study; the majority are from SME1.

The following assumptions are made about the die sort data and model formulation based on expert input from SDSS and the wafer fabrication process engineers. The wafers originate at multiple fabrication facilities (within the same site). Fabs are not separated by location since the assumption at the time was that processes and materials mix between locations so often that the resulting wafers are interchangeable.

The model ignores wafer spatial location and radial distance and just focuses on the input die sort parameter data alone. As discussed later in Chapter 8, calculating spatial indicators could be a promising next step. At this time, there is no access to a comprehensive reference list of each parameter and its meaning, obsolescence, or thresholds. Thus, logic rules about parameters are not implemented, such as dependencies between parameters, excluding irrelevant parameters, or grouping parameters. Lastly, the die are treated as independent units. A next step could be to create a nested structure where die are nested within wafers and wafers nested within lots in order to represent these relationships, as described in the data preparation methodology of Krueger [13].

#### 4.2.2 Known Good Die Data

KGD data results are taken from a separate, live test system and the data is aggregated and sent to the data repository. During the KGD test program execution, there are hundreds of potential soft bins. Each die can land in only one soft bin and each test item occurs in chronological order. This model assumes that any untested bins would pass since once a die

fails a test item it does not continue the rest of the tests. This optimizes test time and is based on the assumption that test items are ordered by importance. As discussed in Chapter 8, there is a potential to explore this assumption to analyze soft bin correlations. KGD data also includes parameters values similar to die sort parameter data. For this study, around 300+ KGD parameters are included.

#### 4.2.3 Memory Test Data

Memory test data is stored in several tables in the data repository. Die-level memory test results exist with an equivalent failure category to KGD soft bins, called FH soft bin or MT test block number. For consistency, it will be referred to as FH soft bin. Similar to KGD soft bins, each die has a binary result. The result is pass/fail and what single FH soft bin it landed in. As discussed in Chapter 8, the potential to reference continuous values would enhance the model but is not available at this time. For example, during memory test program execution, a bad block count accumulates for each die as it moves through each test item. There exists a cutoff value and if the bad block count exceeds this threshold, the die is identified as a fail and the die is not tested further in order to optimize test time. The test item when the fail occurred is identified as the FH soft bin. Thus, FH soft bin is a limited response variable since it contains little insight into the exact failure mode.

For this study, FH is the memory test step examined. For the memory test prediction model, specific memory test programs have been selected based on expert input. KGD programs are not filtered but assumed to be equivalent; this hypothesis could be explored further as discussed in Chapter 8.

# Chapter 5

# Model Development and Results

Chapter 5 summarizes the prediction models and analyzes the accuracy of the prediction results. Section 5.1 describes the methodologies developed while creating the prediction model, including data refining and evaluation metrics. Sections 5.2-5.4 cover the wafer-level KGD, die-level KGD, and die-level memory test prediction results. Section 5.5 summarizes the main results from the models.

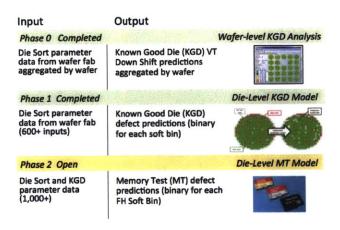

Model development proceeds in three phases. First, a wafer-level proof of concept analysis predicts KGD failures based on SME1 data. Second, a die-level model predicts KGD failures based on SME1 data. Third, a die-level model is developed to predict MT fails based on SME1, SME2, and KGD parameter data. The general development strategy first focuses on predicting KGD results and then applying the lessons learned to the more complex MT model.

For each model, a specific technology, memory size (e.g., 64GB, 128GB), test program, and product are targeted. Collaboration with the relevant experts and data owners resulted in the model logic and data refining techniques described below.

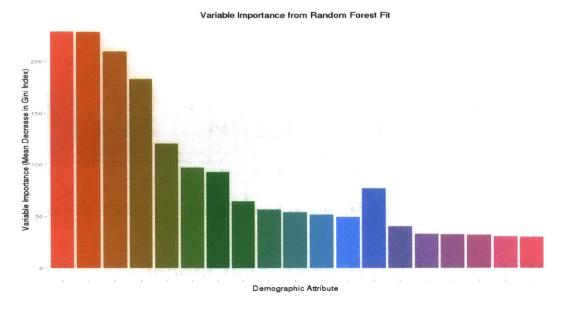

## 5.1 Model Preparation

For all models, performance is evaluated with metrics of confusion matrices and receiver operating characteristics (ROC) curve. Recent historical production data is analyzed. Top soft bins and expert input determined which soft bins to select. Die-level granularity is

Figure 5-1: Summary of model approach phases

targeted since wafer-level analysis would not be useful for MT improvements. Plane-level analysis (there can be 1, 2, or 3 planes per die) would be a possible next step but at this time are assumed to not add as much manufacturing process improvement opportunities as identifying defective units at the die-level.

#### 5.1.1 Data Refining Approach

The following describes the general methodology for data cleansing used to prepare the merged data sets of die sort, KGD, and MT test data. R Studio is used but other tools would be just as suitable, such as Python or a SQL database. Although rare, entire duplicate rows were removed. Any missing or null values are analyzed to determine if the entire field should be removed (majority of samples had null values) or just small numbers of samples that had data inconsistencies (very few samples had missing values for unknown reasons). Parameters with non-numeric values are excluded. Engineering input determined that outliers should remain and so the data set is left as is since data anomalies could be indicative of actual deviations. Samples per test date are plotted to ensure random, adequate samples over time (for the MT model). Engineering input determined that input parameters should all remain as is. Lastly, a sanity check of the number of lots (wafer lots, memory test lots), wafers, dies, defects, and remaining date ranges is performed before saving as a data frame in memory for processing.

The resulting data set is then filtered to focus on a specific device (technology), test

program, test step, SME1 date range, MT date range (for MT model), and part number (for KGD model) in order to compare samples that have the same test procedures and manufacturing flow. In the memory test data set, samples are removed that were KGD failures since they would have no MT response variable. In the MT model, samples are removed that engineering experts identified as not relevant to the analysis. Lastly, any other fields are removed (besides the response variable) that would not exist at the time a prediction would be made, such as hard bin.

A defect Pareto is next created to identify the top failure categories (soft bins). Engineering experts reviewed the top categories and the response variable, KGD or FH soft bin, is selected. For the MT model, FH soft bins are combined based on expert advice. All samples but the selected soft bin are updated to pass records. Only samples with the selected fail mode are designated by a binary "1" and all others (even samples that had a different fail mode) are designated by a binary "0". This model thus uses a binary classifier; Chapter 8 explores further methodologies to improve this categorization.

Next, the data set is randomly split into training and testing sets, split randomly twothirds training and one-third testing. For a sub-analysis described in Section 5.4, the data set is split into training, testing, and validation sets. The validation set contained samples from a separate memory test date range to explore the impact of a separate time frame on the prediction results. The randomness of the split is verified by ensuring that there is roughly the same distribution between training and test sets of the percentage of failures. In cases where computational limits are anticipated to be an issue for the training set model formulation, pass records are randomly sampled (oversampling of the rare defect samples). This methodology will be described later in Section 5.4. Fewer samples in the training set results in a higher impact on the probability of overkill such that there are more extreme fluctuations of prediction accuracy. Experimentation with this data set shows that the number of pass records needs to be at least five times the number of failures to train a model that can reach optimal results. Thus, sampling the pass records is found to be a helpful methodology during initial development phase to speed up computation and still find a meaningful prediction level. Experimentation shows that at least several hundred fail samples are needed in the training set to obtain meaningful predictions.

| Example test set |        | <pre>&gt; confusion.matrix(testing\$MT_Fail,var_predict,.8)</pre> |        |       |      |       |                  |                 |

|------------------|--------|-------------------------------------------------------------------|--------|-------|------|-------|------------------|-----------------|

| real fails       | 3000   | obs                                                               |        |       |      |       |                  | 80% Probability |

| real pass        | 300000 | pred                                                              | 9      | 1   [ | 900  | 30.0% | underkill        | ]               |

|                  |        | 0                                                                 | 299900 | 900   | 100  | 0.03% | overkill         | 1               |

|                  |        | 1                                                                 | 100    | 2100  | 2100 | 70.0% | correct defects  | 1               |

|                  |        |                                                                   |        |       |      | 0.048 | Overkill/Correct | Defect Ratio    |

Figure 5-2: Example confusion matrix

#### 5.1.2 Evaluation Metrics

The main evaluation metrics considered here are confusion matrices and receiver operating characteristic (ROC) to visualize model performance. Confusion matrices are calculated at probabilities ranging from 0.05, .1, .2, ... to .9 and manually analyzed to determine the optimal results.

In this model, there is a binary response variable. "0" indicates pass (negative for defect condition) and "1" indicates defect (positive for defect condition). In a confusion matrix generated in the R package SDMTools with confusion.matrix command [28], there are four values as shown in Figure 5-2. The top left is a predicted pass and actual pass (true negative, "specificity"). The top right is a predicted pass and actual fail (false negative, type II error,  $\beta$ , or "underkill"). The bottom left is a predicted fail and actual pass (false positive, type I error,  $\alpha$ , or "overkill"). The bottom right is a predicted fail and actual fail (true positive, "sensitivity").

In Figure 5-2, the example confusion matrix shows the testing data set contains 303,000 samples, of which 3,000 are actual fails. After applying the trained prediction model to the test set, this confusion matrix is obtained. The prediction results in 299,900 true negatives, 900 underkill, 100 overkill, and 2,100 true negatives. The prediction identifies 2,100 defects correctly (70 percent) and misses 900 (30 percent). It also labels 100 as defects that are actual passes.

The confusion matrix in Figure 5-2 also introduces the concept of a threshold. The threshold is the third parameter input for the *SDMTools* package's *confusion.matrix* command after the testing set prediction model is complete [28]. Thresholds range from 0 to 1 and conceptually represent a likelihood. The particular results in Figure 5-2 correspond

Figure 5-3: Example receiver operating characteristic (ROC) in R

to a threshold of 0.8. Threshold determines the sensitivity and specificity. Sensitivity is defined as the percentage of true positives (correct defect predictions). Sensitivity equals one minus Type II errors. Specificity is defined as the percentage of true negatives (correct pass predictions). Type I errors equal one minus the specificity [11]. Thus, alternative confusion matrices result when the threshold is changed. This threshold controls the expected incorrect predictions, which is a trade-off between false positives and false negatives. At higher threshold levels, false positives are reduced (defect prediction is more accurate) but false negatives increase (fewer defects are identified). At lower thresholds, false positives increase and false negatives decrease.

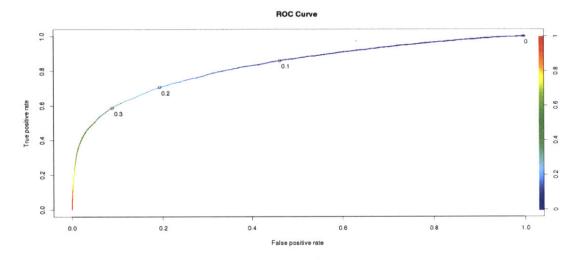

A receiver operating characteristic (ROC) curve visualizes the trade-off between the false positive rate (x-axis) and true positive rate (y-axis) at every threshold. The total performance of a classifier, summarized across all thresholds, is the area under the ROC curve (AUC). An ideal ROC curve would fit into the top left corner of the plot and maximize the AUC. This scenario represents a high true positive rate and low false positive rate. An ROC of a random guess would be a straight line from the bottom left to top right of the plot. ROC curves are a popular graphic since they simultaneously display both error types and consider all possible thresholds [11].

Figure 5-3 is an example ROC curve generated with the R package *ROCR* to compare model results [24]. A threshold of 0.8 lands in the orange portion of the curve in the

bottom left corner. At this threshold, false positives are minimized under one percent. As a trade-off, true positives remain around ten percent. Therefore, false negatives are around ninety percent. This example calls attention to another prediction modeling challenge of how to determine the appropriate threshold for future predictions. Namely, what threshold accurately represents the trade-off between false positives (lost revenue) and true positives (avoided cost)?

The rates of false false negatives, false positives, and true negatives alone do not provide the full picture. R squared is another metric that can be calculated with the prediction results, but does not provide enough insight into the prediction accuracy across thresholds to be a meaningful evaluation metric. Due to the small percentage of defects in the population, a metric of solely false positive rate will invariably be very small and misleading. In terms of incorporating business requirements, one hundred percent false negatives already exist in the manufacturing process as these are currently not caught in the status quo quality measures. On the other hand, false positives cannot be accepted since it represents wasted wafers or die. This waste represents lost revenue as this material would have been assembled into prime products if the prediction had not falsely flagged the unit as a defect. Given the high production cost already invested in these units by the time they arrive at assembly, there is a very low risk tolerance for any false positives.

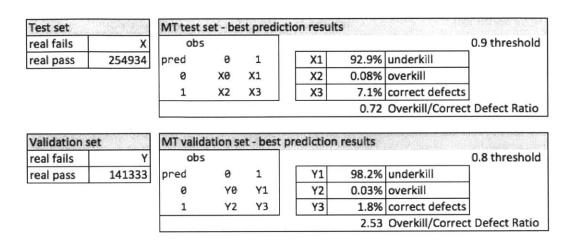

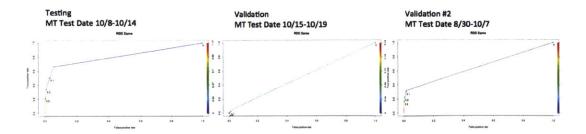

This paper proposes a false positive ("overkill") to true negatives (correct defect predictions) ratio as an evaluation metric and recommendations are described in Section 6.1. This "overkill/correct defect ratio" compares the magnitude of false positives to true negatives. This ratio is a meaningful way to compare different prediction model results and determine the appropriate threshold value. For example, in Figure 5-2 an "overkill/correct defect ratio" of 0.048 is displayed (100/2100). If this ratio reaches one (2100 "overkill" and 2100 correct defect predictions), the prediction model would not make financial sense to implement since the number of false positives would reach the number of actual correct predictions. An appropriate ratio threshold can be set by the company based on the relative cost trade-offs between lost revenue of a wasted unit and cost avoidance savings of predicting defects.