## p-GaN Platform for Next-Generation GaN Complementary Transistors and Circuits

by

### Qingyun Xie

### B.S., Cornell University (2016) S.M., Massachusetts Institute of Technology (2020)

#### Submitted to the Department of Electrical Engineering and Computer Science in partial fulfillment of the requirements for the degree of

#### DOCTOR OF PHILOSOPHY

at the

#### MASSACHUSETTS INSTITUTE OF TECHNOLOGY

February 2024

© 2024 Qingyun Xie. All rights reserved.

The author hereby grants to MIT a nonexclusive, worldwide, irrevocable, royalty-free license to exercise any and all rights under copyright, including to reproduce, preserve, distribute and publicly display copies of the thesis, or release the thesis under an open-access license.

| Authored by:  | Qingyun Xie<br>Department of Electrical Engineering and Computer Science<br>December 20, 2023                                          |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------|

| Certified by: | Tomás Palacios<br>Clarence J. LeBel Professor of Electrical Engineering and Computer Science<br>Thesis Supervisor                      |

| Accepted by:  | Leslie A. Kolodziejski<br>Professor of Electrical Engineering and Computer Science<br>Chair, Department Committee on Graduate Students |

### p-GaN Platform for Next-Generation GaN Complementary Transistors and Circuits

by

#### Qingyun Xie

Submitted to the Department of Electrical Engineering and Computer Science on December 20, 2023 in partial fulfillment of the requirements for the degree of

#### DOCTOR OF PHILOSOPHY

#### ABSTRACT

Gallium nitride (GaN) integrated circuits (ICs) are receiving increasing attention because they offer compactness, reduced parasitics, and higher performance compared to discrete transistors or printed circuit board (PCB) integration. The p-GaN platform exhibits tremendous potential in power ICs and recently, in high temperature (500 °C) digital circuits. While the initial demonstrations offer promising results, several challenges remain. Notably, the lack of a monolithically integrated GaN complementary technology impedes the advancement of GaN power ICs.

This thesis aims to enhance the p-GaN platform (GaN-CMOS platform) (CMOS: complementary metal-oxide-semiconductor) through developing the next generation of GaN complementary technology (p-channel and n-channel field-effect transistors (FETs)). Based on the GaN-CMOS platform, the aggressive scaling of novel complementary transistors (self-aligned-gate p-FET and self-aligned metal/p-GaN-gate HEMT) is pursued. Alternative metallization schemes and a new technology for gate recess in GaN p-FETs are demonstrated. The unique characteristics of the p-FET are revealed through a combination of experimental measurements and TCAD simulations. The p-FET (based on GaN-CMOS platform) and p-GaN-gate n-FETs are analyzed for high temperature operation. Lastly, in order to aid the future design of more complex circuits based on the p-GaN platform, a device-to-circuit CAD framework was developed for GaN n-FET circuits and validated at high temperature up to 500 °C.

To the best of the author's knowledge, the above results represent the state-of-the-art in GaN complementary technology and GaN electronics based on the p-GaN platform. These findings are expected to deliver wider impact in the areas of power, RF/mixed-signal, and high temperature electronics.

Thesis supervisor: Tomás Palacios Title: Clarence J. LeBel Professor of Electrical Engineering and Computer Science

# Acknowledgments

Looking back, my Ph.D. studies has been a long but rewarding journey. I am deeply indebted to have had the opportunity to pursue cutting-edge research in an intellectually stimulating environment and leading institution. The thesis is a testament to the accomplishments of the research, as well as the mentorship and guidance I have received throughout the years.

First and foremost, I would like to express my sincerest gratitude to my thesis supervisor, Professor Tomás Palacios. Despite his busy schedule, he was extremely generous with his time and effort to offer insightful advice on my thesis. He has offered a wealth of resources to the research, therefore ensuring that the student need not worry about logistical and funding issues. He offered inspiration and support in every step of the Ph.D. journey. He consistently encouraged me to be focused, visionary and motivated on research in GaN electronics, even during the most difficult times of my Ph.D. journey (including the COVID-related disruptions which impacted for more than a year). He has upheld rigorous academic standards and high expectations of state-of-the-art research, while being extremely caring, understanding and flexibility in many circumstances. I shall forever remember him as a key mentor in my academic career, and I strive to carry such high standards in my future work.

I am grateful to the unwavering support of the other members of the thesis committee, Professor Jesús A. del Alamo and Professor Negar Reiskarimian. They have offered their insightful advice on their areas of expertise, many of which are highly relevant to this thesis, including p-GaN-gate HEMTs, transistor design trade-offs, characterization, and compact modeling for circuits. The inclusion of their diverse views has broadened the scope of the thesis to make it more valuable for

the broader research community. Special mention to Dr. Jeffrey H. Lang, my academic advisor, for his consistent guidance on my Ph.D. milestones and timeline. His invaluable advice has allowed me to navigate through the Ph.D. journey.

In this day and age, research is not a "one-man band," but instead requires extensive collective efforts to address some of the most complex problems in science and engineering. I am immensely fortunate to have established extensive collaborations with many talented researchers at MIT and in external institutions. Special mention to:

- Dr. Nadim Chowdhury (first graduate student at MIT, and presently, Asst. Professor, Dept. of EEE, Bangladesh University of Engineering and Technology). Dr. Chowdhury has been instrumental to my Ph.D. journey and has offered immense guidance to me. When he was a senior student, he introduced me to the world of GaN electronics, in particular GaN-CMOS. At BUET, he has consistently offered fresh perspectives on my thesis, by taking advantage of his extensive interactions with the industry and academic community. My collaboration with BUET, under the joint supervision of Dr. Palacios and Dr. Chowdhury, has been extremely fruitful. BUET has offered significant complementary expertise in TCAD simulation and modeling, as attested by several collaborative publications. Other collaborators at BUET are gratefully acknowledged, including Mr. Bejoy Sikder (Lecturer, Dept. of EEE, BUET), Mr. Toiyob Hossain, Mr. Ayan Biswas Pranta, Mr. Abdullah Jubair Bin Iqbal, Mr. Rafid Hassan Palash, and others.

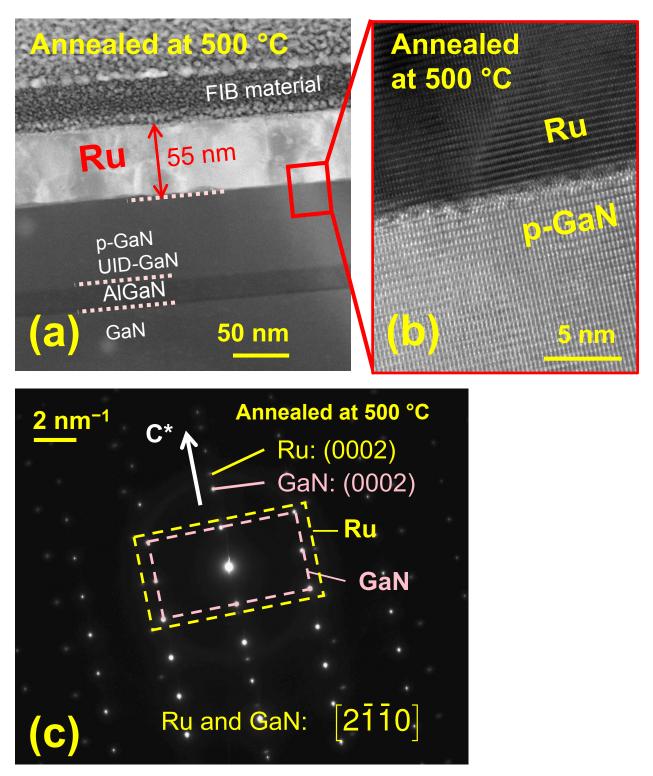

- Dr. Nitul S. Rajput, Sr. Researcher, Advanced Materials Research Center, Technology Innovation Institute, U.A.E. Dr. Rajput has devoted enormous time and effort in the advanced microscopy investigation of our devices. He generously shares his wealth of knowledge on material characterization and analysis. This rewarding collaboration has offered an insightful and complementary aspect to the GaN electronics research.

- Mr. John Niroula, Dr. Mengyang Yuan, Dr. Pao-Chuan Shih, current and former graduate students at MIT. They have offered significant guidance and support to me in the areas of

device design, fabrication, and characterization. I have benefited tremendously from the inspiring discussions with them. They have made significant (and often, complementary) contributions to this thesis, whether directly or indirectly.

Other fruitful collaborations and discussions with Dr. Yuhao Zhang (Dept. of ECE, Virginia Polytechnic Institute and State University (Virginia Tech)), Dr. Yuji Zhao, Mr. Shisong Luo (Dept. of ECE, Rice University), Dr. Kai Fu (Dept. of ECE, University of Utah), Dr. Cheng Zhang (Dept. of EEE, University of Manchester), Dr. Siddharth Rajan, Mr. Sheikh Ifatur Rahman (Dept. of ECE, Ohio State University), Dr. Debbie G. Senesky (Dept. of Aeronautics and Astronautics, Stanford University), and Dr. Savannah R. Eisner (Dept. of EE, Columbia University) are gratefully acknowledged.

I would like to thank the current and former members of Palacios Group. Ms. Preetha Kingsview has provided amazing administrative support and guidance in many aspects of my life at MIT. Dr. Yuhao Zhang, Dr. Daniel Piedra, Dr. Ahmad Zubair, Dr. Jori Lemettinen, Dr. Nadim Chowdhury, Dr. Mengyang Yuan, Dr. Pao-Chuan Shih, and Mr. Miguel Sánchez Lozano; Mr. Joshua A. Perozek, Mr. John Niroula, Ms. Jung-Han Hsia, Mr. Pradyot Yadav, Ms. Hridibrata Pal, Mr. Minsik Oh, Ms. Gillian K. Micale, Mr. Patrick K. Darmawi-Iskandar, and Mr. James A. Greer; Dr. Xu Zhang, Dr. Yuxuan Lin, Dr. Marek Hempel, Dr. Elaine D. McVay, and Dr. Mantian Xue; Mr. Jiadi Zhu, Mr. Christian E. López Ángeles, Ms. Hae Won Lee, Mr. Yixuan Jiao, Mr. Ayush Gupta, Ms. Aijia Yao, and Mr. Michal Prokop.

This thesis research is highly dependent on the world-class nano-fabrication and characterization facilities at MIT.nano. I am immensely grateful to the guidance and support of all staff members of MIT.nano. I would like to give special mention to Dr. Jorg Scholvin (Associate Director, MIT.nano). Besides navigating me through MIT.nano, he has always encouraged me to deepen my understanding of transistors through thoughtful nano-fabrication experiments, therefore adding another dimension (besides the demonstrations of state-of-the-art transistors) to this thesis. I would like to thank Mr. Kristofor Payer, Mr. David M. Terry, Mr. Kurt A. Broderick, Mr. Robert J. Bicchieri, Mr. Mark K. Mondol, Mr. Dennis Ward, Mr. Eric Lim, Mr. Donal Jamieson, Dr. Juan Ferrera, Dr. Hanqing Li, Ms. Maansi Patel, Mr. Gary Riggott, Mr. Scott Poesse, Mr. Paul S. Tierney, Mr. James M. Daley, Dr. Elham Rafie Borujeny, Dr. Aubrey Penn, Mr. Daniel A. Adams, Mr. Paul J. McGrath, Dr. Vicky Diadiuk, Mr. Michael B. McIlrath, Mr. Mike Hobbs, Mr. Bill Maloney, and Mr. Joseph S. C. Baylon.

This thesis would not have been possible without several sponsored research projects, including Samsung Electronics Co., Ltd. Award No. 033517-00001 (monitored by Dr. Jongseob Kim and Dr. Jaejoon Oh), Qualcomm Inc. Award No. MAS-492857 (monitored by Dr. Ranadeep Dutta), and International Business Machines Corp. (IBM) award (monitored by Dr. Dirk Pfeiffer). III-N epitaxial wafers were provided by Enkris Semiconductor, Inc. (Dr. Kai Cheng), Samsung Electronics Co., Ltd. (Dr. Jongseob Kim, Ms. Boram Kim), and MIT Lincoln Laboratory (Dr. Richard J. Molnar, Mr. Tom Osadchy). Part of the research was conducted at external experimental facilities, including Center for Materials, Devices, and Integrated Systems (CMDIS), Rensselaer Polytechnic Institute (Mr. Bryant C. Colwill, Dr. Xiaohong An); Center for Nanoscale Systems, Harvard University; Advanced Materials Research Center, Technology Innovation Institute (Dr. Nitul S. Rajput), U.A.E.; Semiconductor Epitaxy and Analysis Laboratory (SEAL), Ohio State University (Prof. Siddharth Rajan, Mr. Sheikh Ifatur Rahman). I would like to express my gratitude to Agency for Science, Technology and Research (A\*STAR) Singapore, and several members of the current and former staff at the Institute of Microelectronics (IME).

I hope to express my heartfelt gratitude to my family members, relatives and friends for their unwavering love and support. This thesis is dedicated to them.

# Contents

| Ti | tle pa  | ge                                                        | 1  |

|----|---------|-----------------------------------------------------------|----|

| Ał | ostrac  | t                                                         | 3  |

| Ac | cknow   | ledgments                                                 | 5  |

| Li | st of I | igures                                                    | 13 |

| Li | st of ] | <b>Fables</b>                                             | 16 |

| 1  | Intr    | oduction                                                  | 17 |

|    | 1.1     | Motivation for GaN-CMOS and High Temperature Electronics  | 18 |

|    |         | 1.1.1 Case Study of the RF Front End                      | 19 |

|    | 1.2     | Early Work on GaN-CMOS                                    | 22 |

|    | 1.3     | GaN-CMOS Platform Used in This Thesis                     | 24 |

|    | 1.4     | Requirements of Next-Generation GaN-CMOS Technology       | 25 |

|    | 1.5     | Objectives and Methodology                                | 28 |

|    | 1.6     | Organization of the Thesis                                | 28 |

| 2  | High    | nly Scaled GaN Complementary Technology                   | 31 |

|    | 2.1     | Introduction                                              | 31 |

|    | 2.2     | Epitaxial Platform and Transistor Architectures of GaN CT | 32 |

|    | 2.3     | GaN p-FET                                                 | 34 |

|   |      | 2.3.1   | Self-Aligned GaN p-FinFET Process Flow                            | 34 |

|---|------|---------|-------------------------------------------------------------------|----|

|   |      | 2.3.2   | Results and Discussion                                            | 38 |

|   | 2.4  | GaN n   | -FET                                                              | 40 |

|   |      | 2.4.1   | Self-Aligned p-GaN-Gate HEMT Process Flow                         | 40 |

|   |      | 2.4.2   | Results and Discussion                                            | 44 |

|   |      | 2.4.3   | Comparison of n-FETs based on the GaN-CMOS platform and a conven- |    |

|   |      |         | tional p-GaN epitaxy                                              | 47 |

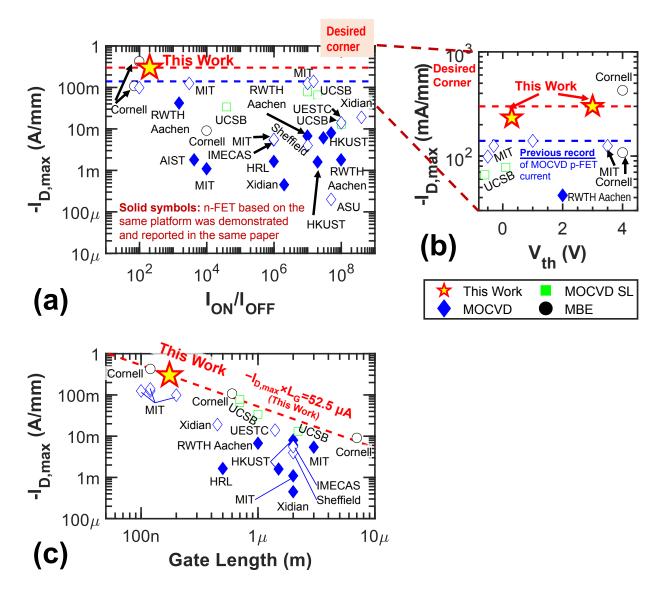

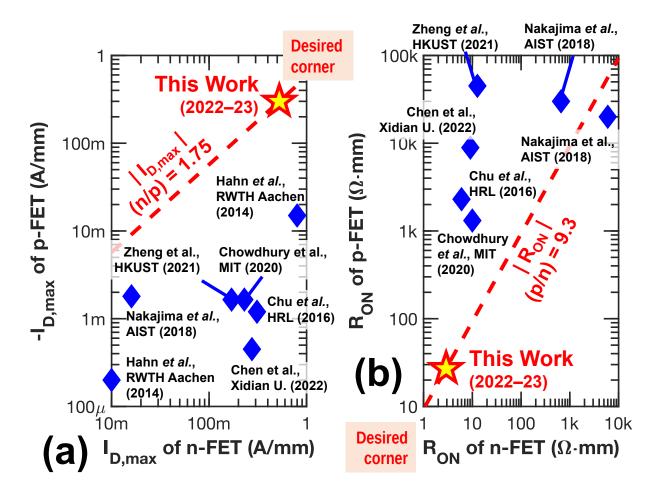

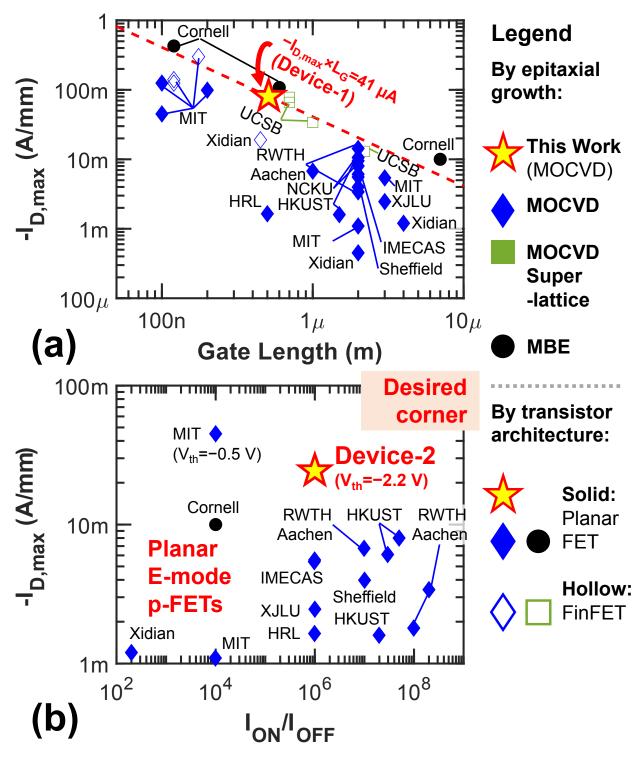

|   | 2.5  | Bench   | marking                                                           | 50 |

|   | 2.6  | Develo  | opment of Improved GaN/AlGaN Selective Etch Recipe                | 56 |

|   | 2.7  | Conclu  | ision                                                             | 62 |

| 3 | Si-C | MOS-C   | Compatible GaN p-FET                                              | 63 |

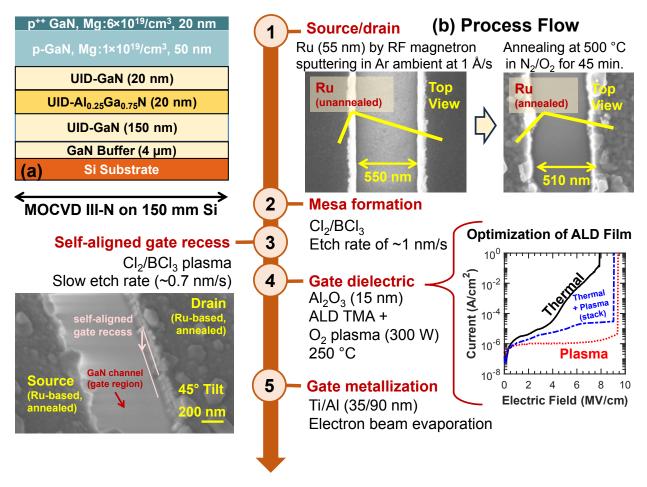

|   | 3.1  | Ru-Ba   | sed Contacts and Their Integration in p-FET                       | 66 |

|   |      | 3.1.1   | Fabrication of p-FET with Ru-Based Contacts                       | 66 |

|   |      | 3.1.2   | Material and Electrical Characterization of Ru-Based Contacts     | 68 |

|   | 3.2  | Transis | stor Performance                                                  | 72 |

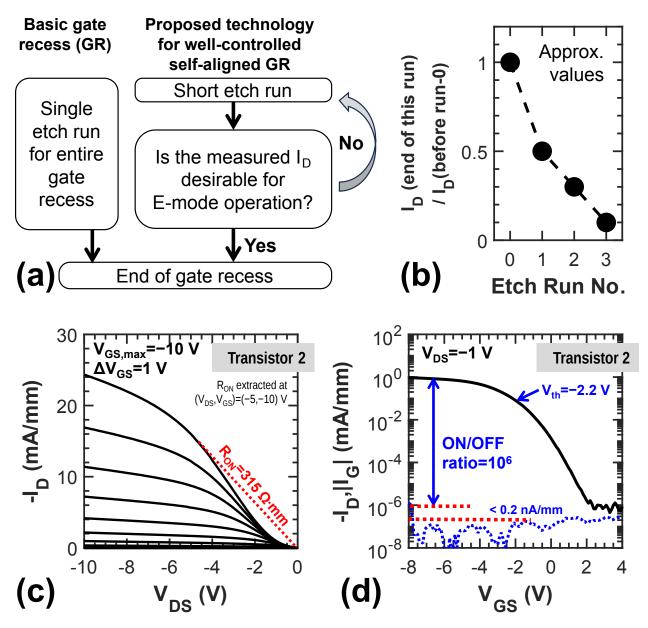

|   |      | 3.2.1   | E-Mode p-FET using Novel Technology for Self-Aligned Gate Recess  | 73 |

|   | 3.3  | Bench   | marking                                                           | 75 |

|   | 3.4  | Conclu  | ision                                                             | 77 |

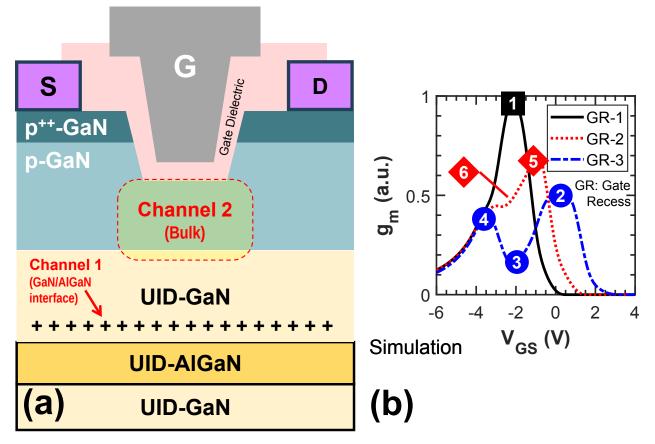

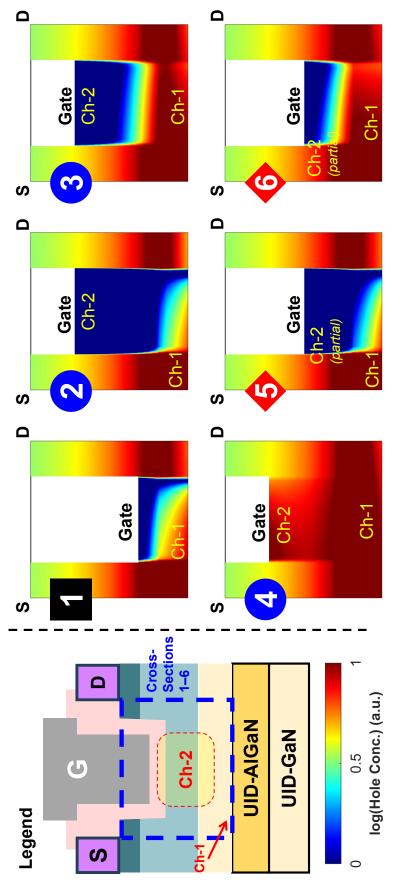

| 4 | Unic | que Des | ign Space of GaN p-FETs                                           | 79 |

|   | 4.1  | Impact  | of Gate Recess on Design Space                                    | 80 |

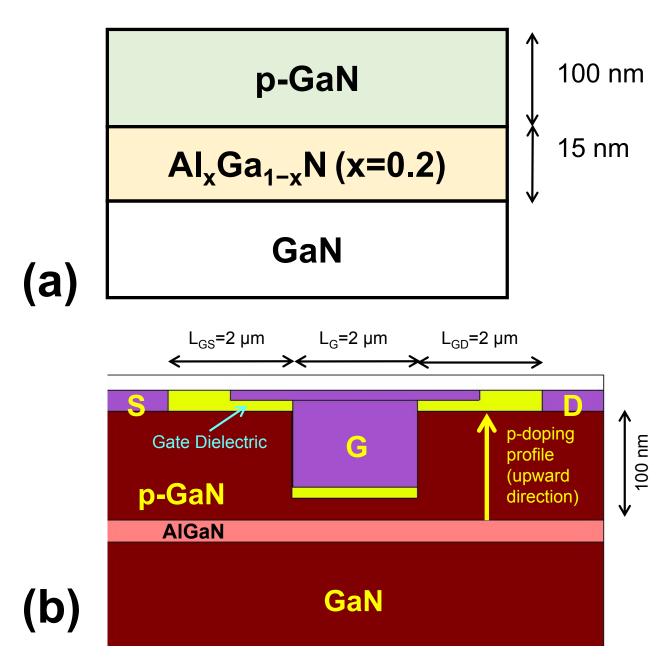

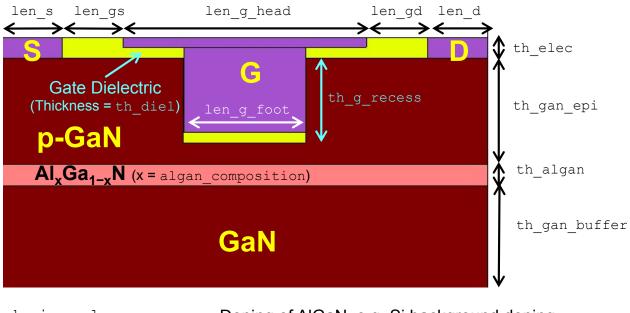

|   |      | 4.1.1   | TCAD Simulation Study of Gate Recess                              | 81 |

|   |      | 4.1.2   | Setup of TCAD Simulation                                          | 81 |

|   |      | 4.1.3   | Simulation Results and Discussion                                 | 84 |

|   |      | 4.1.4   | Experimental Verification of TCAD Predictions                     | 86 |

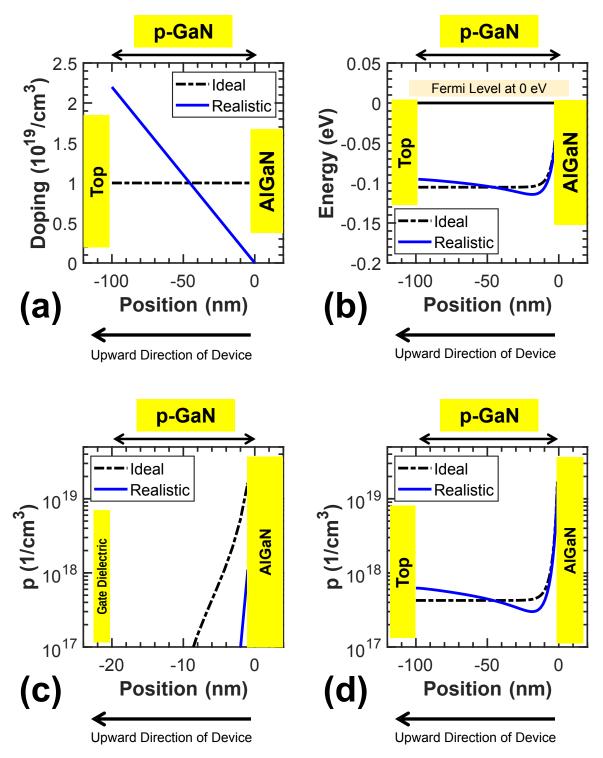

|   | 4.2  | Impact  | of p-GaN Doping Profile                                           | 88 |

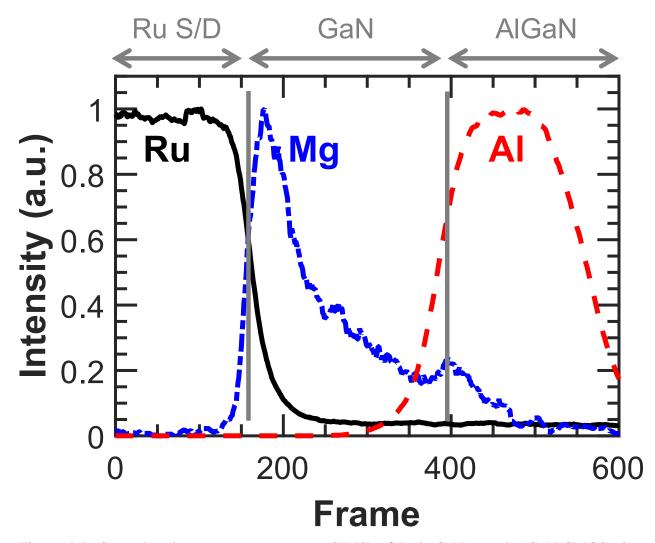

|   |      | 4.2.1   | SIMS Profile of Mg Doping in p-GaN                                | 89 |

|   |      | 4.2.2 Impact on the Performance of the p-FET (Simulation Study) 90              |

|---|------|---------------------------------------------------------------------------------|

|   | 4.3  | Conclusion                                                                      |

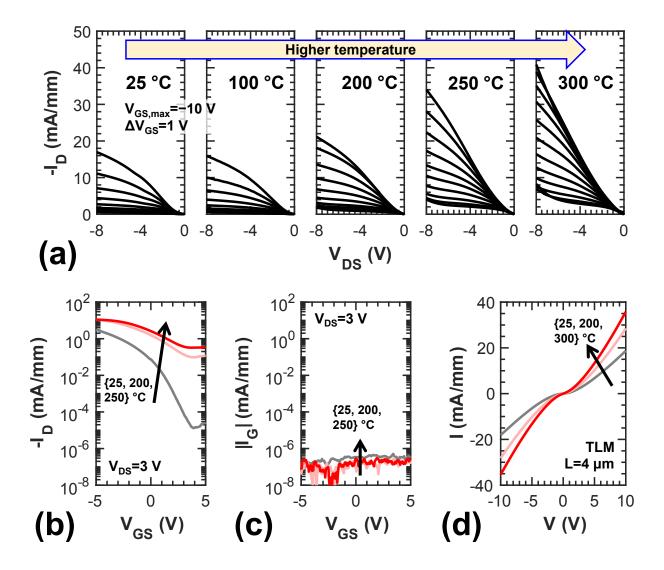

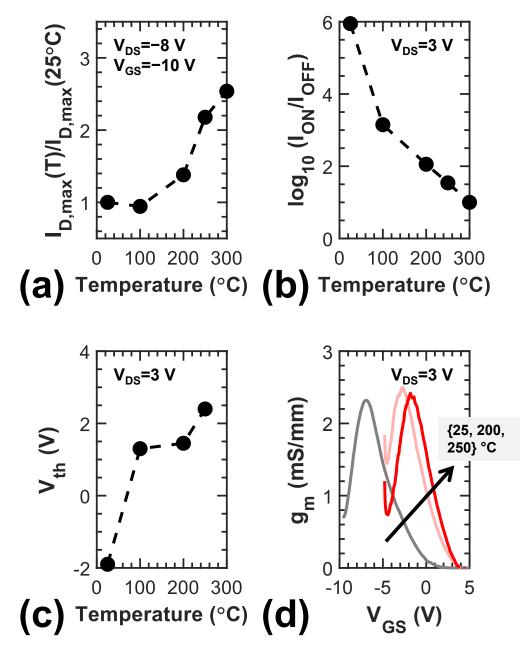

| 5 | p-Fl | ETs and n-FETs for High Temperature Operation 99                                |

|   | 5.1  | High Temperature Performance of GaN p-FETs                                      |

|   |      | 5.1.1 Analysis of Transistor Metrics                                            |

|   |      | 5.1.2 $g_m$ Characteristics                                                     |

|   |      | 5.1.3 Re-examining the Explanations Based on Material Characterization 103      |

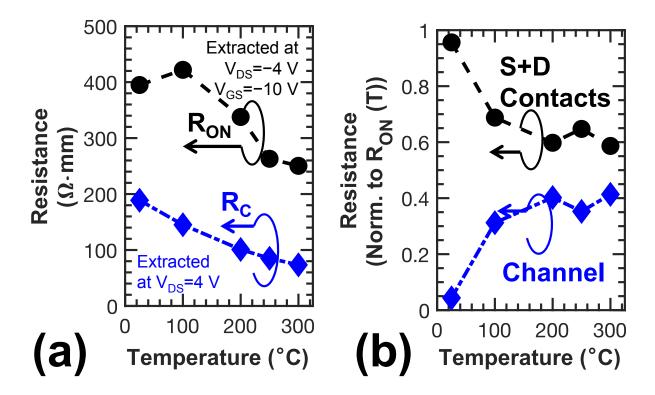

|   |      | 5.1.4 Components of ON-Resistance                                               |

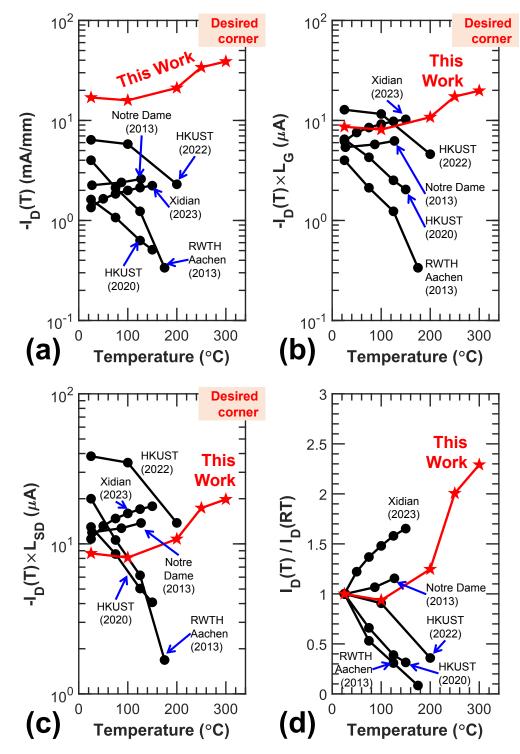

|   |      | 5.1.5 Benchmarking of p-FET Performance at High Temperature                     |

|   |      | 5.1.6 Summary on High Temperature Performance of p-FETs                         |

|   | 5.2  | HT robustness of n-FETs                                                         |

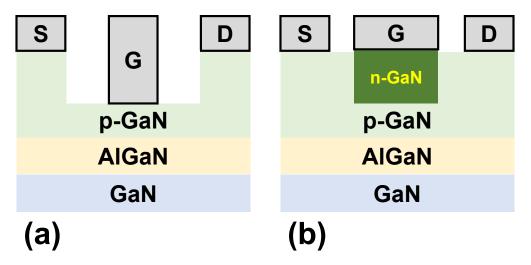

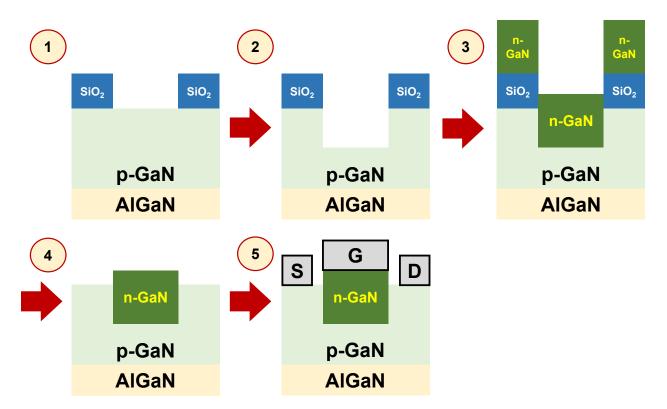

|   | 5.3  | Exploration of Alternative Transistor Structures for High Temperature Robust p- |

|   |      | <b>FETs</b>                                                                     |

|   | 5.4  | Conclusion                                                                      |

| 6 | Tow  | ards DTCO in high temperature GaN-on-Si technology: a CAD framework up to       |

|   | 500  | °C 115                                                                          |

|   | 6.1  | Introduction                                                                    |

|   | 6.2  | Technology Foundation                                                           |

|   | 6.3  | Methodology                                                                     |

|   | 6.4  | Experimentally Verified CAD Framework for HT GaN-on-Si Technology 120           |

|   | 6.5  | Benchmarking and Conclusion                                                     |

| 7 | Con  | clusion and Future Work 127                                                     |

|   | 7.1  | Summary of the Thesis                                                           |

|   | 7.2  | Future Work                                                                     |

|   |      | 7.2.1 Advancing GaN p-FETs and GaN-CMOS                                         |

|   |      | 7.2.2 Circuit-level prototyping of GaN-CMOS                                     |

|    | 7.2.3        | Enhancing the Simulation Framework | 133 |

|----|--------------|------------------------------------|-----|

| A  | Process Flo  | ws                                 | 135 |

| B  | Simulation   | Deck for p-FET                     | 143 |

| Bi | Bibliography |                                    | 151 |

# **List of Figures**

| 1.1  | Applications of GaN-CMOS technology in the RF front end.                         | 21 |

|------|----------------------------------------------------------------------------------|----|

| 1.2  | GaN-CMOS platform.                                                               | 24 |

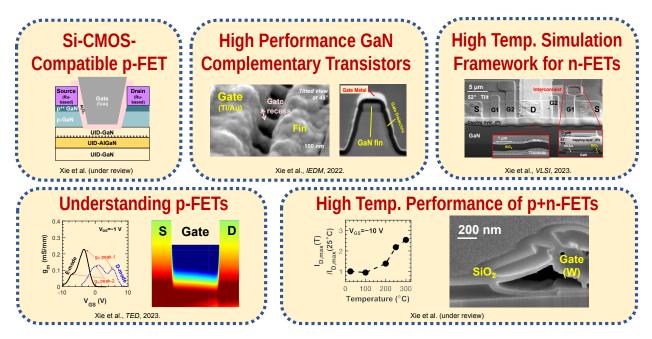

| 1.3  | Advancing next-generation GaN-CMOS technology.                                   | 26 |

| 2.1  | Highly-scaled GaN complementary technology (CT).                                 | 35 |

| 2.2  | Process flow of the self-aligned (SA) FinFET                                     | 36 |

| 2.3  | Performance of self-aligned p-FET.                                               | 39 |

| 2.4  | Systematic study of the impact of fin width and gate recess depth on the perfor- |    |

|      | mance of GaN p-FinFETs.                                                          | 40 |

| 2.5  | Process flow of self-aligned W/p-GaN-gate n-FET.                                 | 41 |

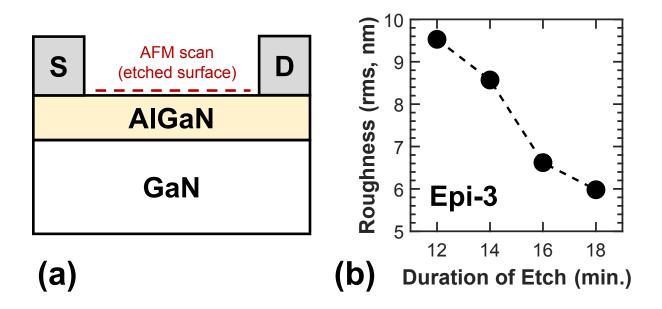

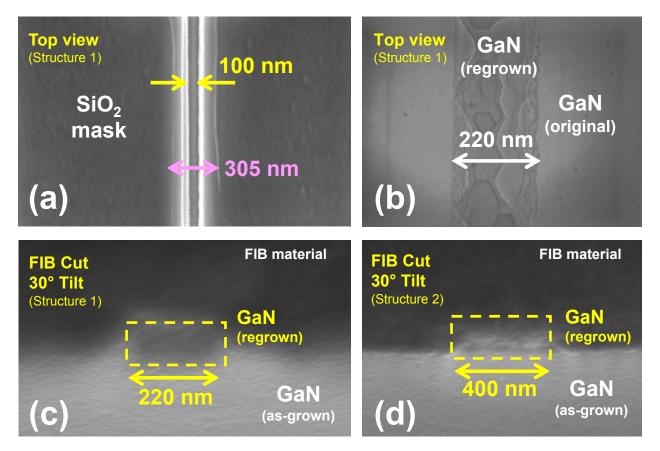

| 2.6  | Selective etch for fabrication of n-FET                                          | 43 |

| 2.7  | Details of fabrication optimization of n-FET (p-GaN-gated AlGaN/GaN HEMT).       | 45 |

| 2.8  | Performance of n-FET fabricated on Epi-1.                                        | 46 |

| 2.9  | Gate length scaling of SA p-GaN-gate n-FETs.                                     | 46 |

| 2.10 | Performance of n-FET fabricated on Epi-2.                                        | 48 |

| 2.11 | Benchmarking of GaN p-FET.                                                       | 51 |

| 2.12 | Benchmarking of n-FET based on the GaN-CMOS platform.                            | 52 |

| 2.13 | Benchmarking of GaN complementary technology.                                    | 53 |

| 2.14 | Epitaxial structures used in the process development of ICP-RIE selective etch   | 56 |

| 2.15 | Process flow used in the development of the ICP-RIE selective etch.              | 57 |

| 2.16 | Process development of the ICP-RIE selective etch (final round of optimization of |     |

|------|-----------------------------------------------------------------------------------|-----|

|      | recipe parameters).                                                               | 58  |

| 2.17 | TLM measurement results of the ohmic contacts fabricated on AlGaN/GaN after       |     |

|      | ICP-RIE selective etch.                                                           | 60  |

| 2.18 | Surface morphology of the AlGaN surface after the ICP-RIE selective etch          | 61  |

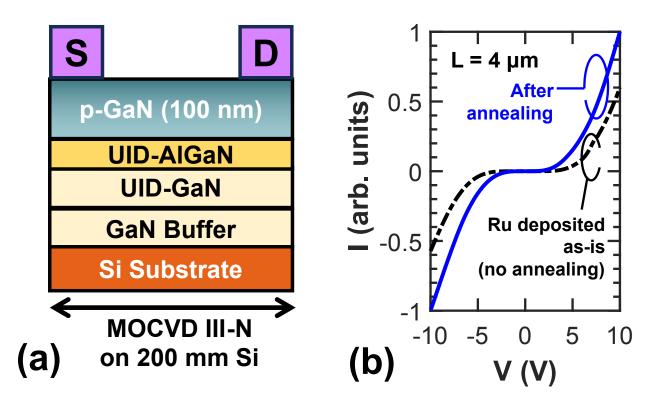

| 3.1  | Process flow of Si-CMOS-compatible GaN p-FETs.                                    | 64  |

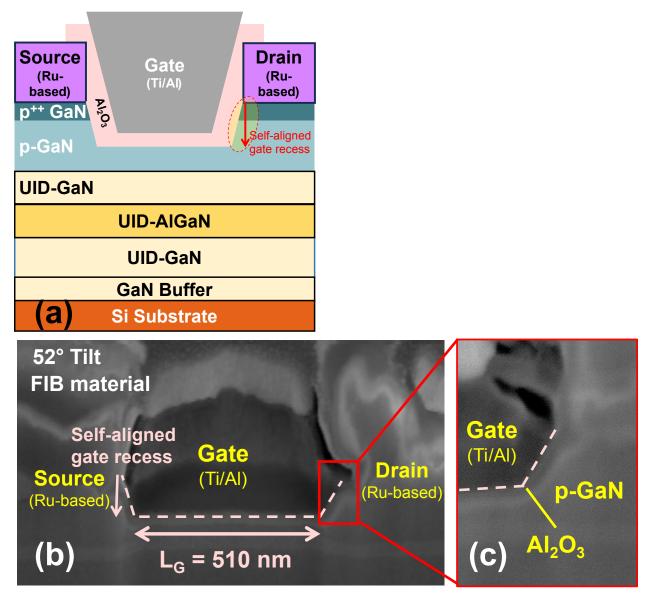

| 3.2  | Si-CMOS-compatible GaN p-channel FETs with Ru-based S/D                           | 65  |

| 3.3  | Microscopy of the Ru-based S/D contacts.                                          | 69  |

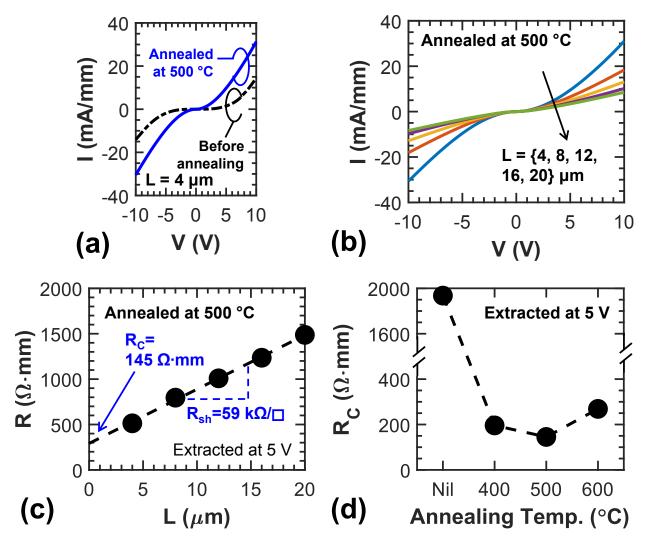

| 3.4  | Electrical characterization of the Ru-based S/D contacts.                         | 70  |

| 3.5  | Ru-based S/D contacts on conventional p-GaN wafer.                                | 71  |

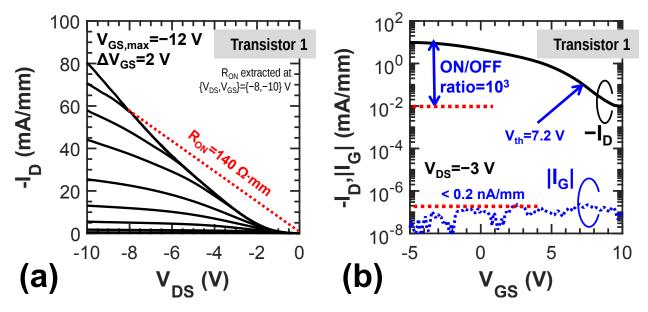

| 3.6  | Performance of a p-FET with Ru-based S/D                                          | 72  |

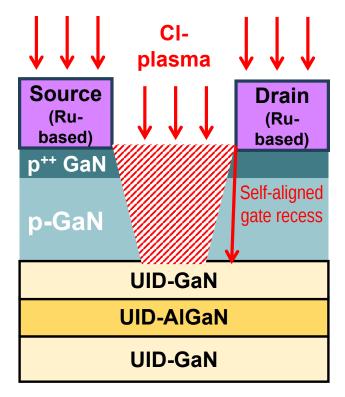

| 3.7  | Schematic illustrating self-aligned gate recess in the p-FET with Ru-based S/D    | 73  |

| 3.8  | E-mode p-FETs with Ru-based S/D using a novel gate recess technology              | 74  |

| 3.9  | Benchmarking of Si-CMOS-Compatible p-FETs.                                        | 76  |

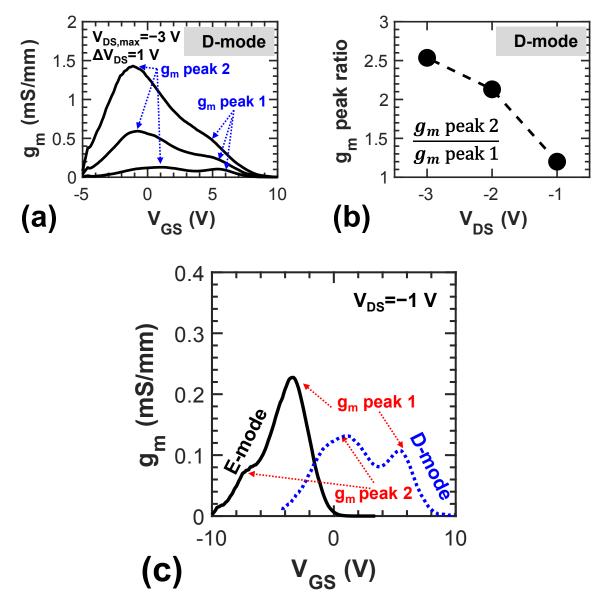

| 4.1  | Unique $g_m$ characteristics of p-FETs with dependency on the gate recess depth   | 82  |

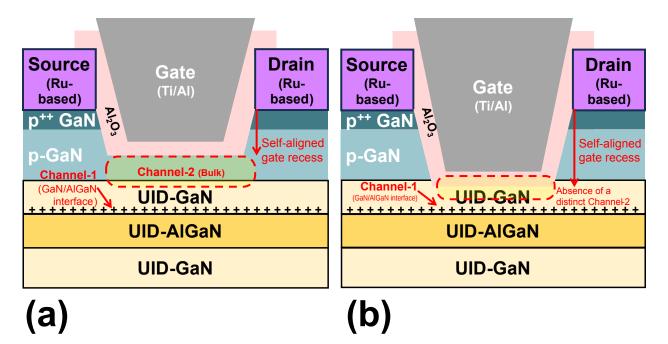

| 4.2  | TCAD simulation of p-FETs to reveal the double $g_m$ peak characteristics         | 83  |

| 4.3  | $g_m$ of a D-mode p-FET and an E-mode p-FET (experimental results of p-FET with   |     |

|      | Ru-based S/D).                                                                    | 87  |

| 4.4  | Device structures of D-mode and E-mode p-FETs with Ru-based S/D                   | 88  |

| 4.5  | SIMS of Ru/p-GaN sample.                                                          | 89  |

| 4.6  | TCAD simulation setup for studying the impact of the p-GaN doping profile         | 92  |

| 4.7  | Impact of a realistic p-GaN doping profile at the material-level                  | 93  |

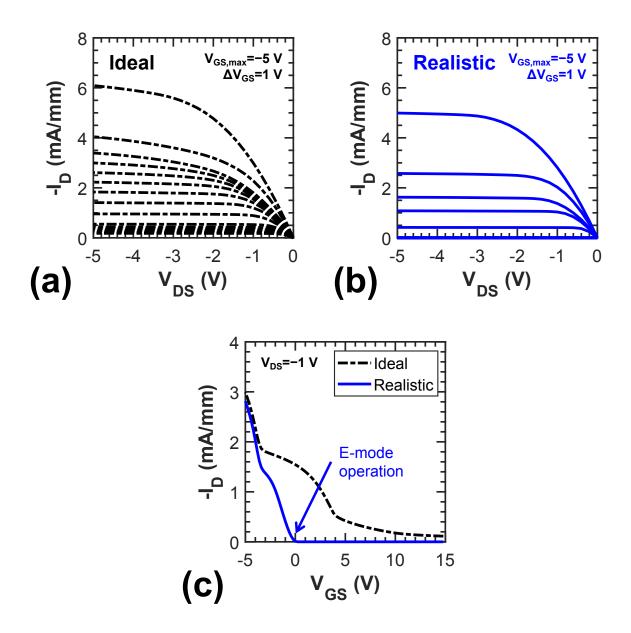

| 4.8  | Simulated DC characteristics of p-FETs with ideal vs. realistic p-GaN doping      |     |

|      | profiles                                                                          | 95  |

| 5.1  | Measurement of a GaN p-FET at high temperature.                                   | 101 |

| 5.2  | Analysis of transistor metrics and $g_m$ at HT                                    | 102 |

| 5.3         | Analysis of components of $R_{ON}$ at HT                                          |

|-------------|-----------------------------------------------------------------------------------|

| 5.4         | Benchmarking of p-FET performance at high temperature                             |

| 5.5         | Concept of the Schottky gate and the junction gate for p-FETs                     |

| 5.6         | Process flow for the proposed GaN p-channel JFET                                  |

| 5.7         | Process development for the short-channel regrowth                                |

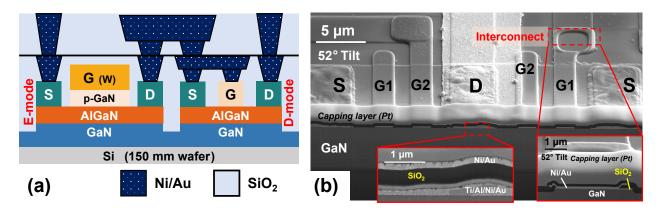

| 6.1         | GaN high temperature technology based on an E/D-mode GaN-on-Si platform 116       |

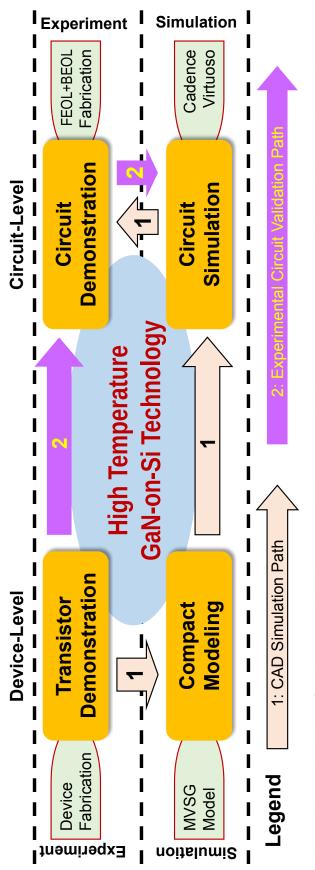

| 6.2         | Methodology for GaN HT technology                                                 |

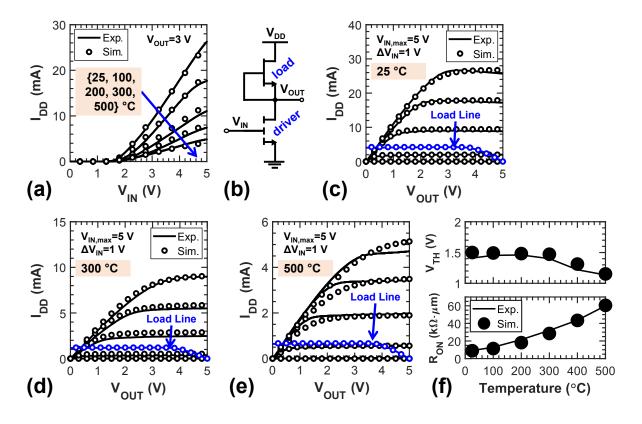

| 6.3         | Characterization and compact modeling of the transistors up to 500 °C             |

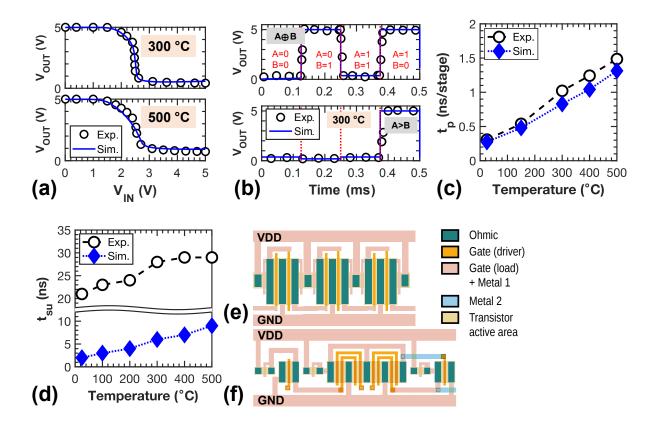

| 6.4         | Experimental validation of the simulation framework at the circuit-level          |

| 7.1         | Key contributions of this thesis                                                  |

| <b>B</b> .1 | Device structure and key parameters of the p-FET in the TCAD simulation setup 143 |

# **List of Tables**

| 2.1 | Benchmarking of GaN complementary technology.                                       | 55  |

|-----|-------------------------------------------------------------------------------------|-----|

| 2.2 | Comparison of the parameters of the optimized ICP-RIE recipe and original RIE       |     |

|     | recipe for selective etch.                                                          | 59  |

| 4.1 | Comparison of the simulated characteristics of the p-FET using a realistic p-doping |     |

|     | profile                                                                             | 94  |

| 6.1 | MVSG model parameters.                                                              | 120 |

| 6.2 | Benchmarking of HT E-Mode GaN HEMTs and their models.                               | 123 |

| 6.3 | Benchmarking of recently published HT GaN circuit simulations.                      | 124 |

# Chapter 1

# Introduction

With the prevalence of electronics in our daily lives and its increasing role in our smart society, the demand for high performance, energy-efficient, compact electronics has seen an exponential increase. While traditionally microelectronics chips have been used for computation, there has been increasing needs for radio frequency (RF) and power electronics for emerging applications such as electric vehicles, 5G/6G telecommunication, and data centers. Among the various semi-conductor technologies, gallium nitride (GaN) stands out as an excellent candidate for *both* RF and power applications, thanks to its wide band gap, high electron mobility, high breakdown field, thermal and chemical stability and more. Since the advent of the first AlGaN/GaN high electron mobility transistor (HEMT) (then called heterostructure field-effect transistor) in 1993, phenomenal advancement has been made the in the field of GaN electronics [1].

In the RF-GaN domain, GaN HEMTs are dominant in the RF power amplifiers in base stations (because only this technology is capable of delivering high power with high power-added efficiency (PAE) at microwave and mm-wave frequencies) [2,3]. Extensive research and development (R&D) efforts are under way to introduce GaN HEMTs for lower voltage applications in the RF front-end of cellular handsets, an application area traditionally dominated by Si LDMOS (laterally-diffused metal-oxide semiconductor) and GaAs pHEMTs (p: pseudomorphic).

In the power-GaN domain, GaN HEMTs promise fast switching with lower parasitics, therefore

greatly reducing the size of the passive components in the power converter [4, 5]. Therefore, GaN HEMTs have gained traction in fast charging power systems (e.g. for EV), as well as compact customer electronics (e.g. laptop/cell phone chargers). Furthermore, the rising performance of GaN power ICs (as opposed to discretely packaged power HEMTs) has offered compactness, and record levels of efficiency and power for data centers, power adapters, electric vehicles (EVs), and 5G telecommunication systems [2, 6, 7].

# **1.1 Motivation for GaN-CMOS and High Temperature Elec**tronics

However, the lack of a GaN p-channel field effect transistor (p-FET) significantly increases static power dissipation (resulting from the use of n-type only enhancement-mode/depletion-mode logic) and prevents all-GaN integration (e.g. control loops, analog mixed-signal blocks) [8]. Power ICs face significant circuit design challenges because classic Si-CMOS gate driving techniques and circuits would not be feasible in all-GaN ICs [9]. On the other hand, the availability of high-side switching GaN p-FETs would improve the switching speed (avoiding the issue of limited common-mode transient immunity (CMTI) in the level shifter), therefore enabling more efficient and higher density power converters [10]. Therefore, the future introduction of GaN p-FETs would greatly benefit (1) mixed-signal integrated circuits, through suppression of static power dissipation [11]; (2) higher speed power converter ICs (e.g. for envelope tracking), by using the p-FET in high-side switching [10]; and (3) in higher linearity Class AB power amplifiers, through compensation of gate capacitance [12]. These applications would significantly improve the performance of GaN-based electronics.

Electronics operating at high temperature (HT), well above the effective 250–300 °C rating of silicon-on-insulator (SOI) technology, is another example of applications for which wide bandgap GaN is uniquely suited. These wide bandgap semiconductors are critical in extreme industrial applications (e.g. jet engines, nuclear reactors, deep oil well drilling), as well as in outer space, from

the solar system to exoplanetary exploration [13, 14]. Owing to inherent limitations of Siliconon-Insulator (SOI) technology (thermal generation of carriers in conventional Si electronics), a promising solution is the use of GaN and other wide band gap materials. Thanks to their wide band gap, and superior electrical, mechanical, and chemical properties, these materials have enabled a wide range of devices. GaN electronics have demonstrated excellent performance in extreme environments (from cryogenic to high temperatures) across RF [15–17], power [18, 19] and mixed-signal applications [20]. Furthermore, much attention has also been paid to GaN-based circuits, mostly for high temperature, based on D-mode n-FETs, [21, 22] E/D-mode n-FETs, [23–25] and E-mode complementary (n+p) FETs. [26, 27] (D: depletion; E: enhancement; FET: fieldeffect transistor) In addition, GaN and III-N materials also offer a wider range of applications in power [28–30], RF [15, 17, 22], MEMS [31–33], memory [34], and solar cells [35]. Given the rapid advancement in GaN device technology for extreme environment applications, it is an opportune time to examine the high temperature performance of emerging GaN transistors such as p-FETs, as well as the harsh environment robustness of more established transistors like the p-GaN-gate HEMT, in order to further optimize these transistors.

#### **1.1.1** Case Study of the RF Front End

Here, the case study of the RF front end, its existing issues and how a proposed GaN-CMOS technology could enable higher performance in the RF front end are discussed.

The realization of a high-data-rate uplink/downlink (peak rates of 10/20 Gbps) for 5G New Radio (NR) and beyond relies on the development of mm-wave transmitters, whose performance is in turn dominated by the linearity and power efficiency of the PAs [36]. Although GaN PAs have delivered unprecedented levels of power at K<sub>a</sub>, W bands and beyond (e.g. 15 dBm at 205 GHz [37]), their limited linearity and the large PAPR in modern modulation schemes force GaN high electron mobility transistors (HEMTs) to operate at more than 6 dB power back-off, which significantly reduces the overall amplifier efficiency. New bottom-up approaches, based on innovations at the device-level, are highly desired to fundamentally improve linearity. Existing device-level techniques focus on the engineering of the transconductance  $(g_m)$  in GaN HEMTs [38–41], but an area that has received little attention is the non-linear gate capacitance, which has been identified to result in significant AM/PM distortion in GaN PAs [42, 43].

The use of a p-FET to compensate the non-linear gate capacitance of RF transistors has been proposed for Si amplifiers [44]. However, the lack of a native p-type device prevents non-Si RF transistors from taking advantage of this technique. Using an existing Si PMOS device in combination with a GaN n-channel transistor leads to (1) complex heterogeneous integration, possibly 3D chip bonding [45], therefore higher parasitics; and (2) limited input voltage swings due to the breakdown voltage of Si PMOS, which will reduce maximum allowable  $P_{in}$  (hence  $P_{out}$ ). Therefore, to retain the existing advantages of GaN HEMTs in PAs, a monolithically integrated GaN p-FET is necessary.

Envelope tracking (ET) has been widely used since 4G LTE to improve the efficiency of PAs and the battery lifetime of cellular handsets [46,47]. In 5G FR2, for a conservative uplink/downlink rate of 1/5 Gbps, even with a high-order modulation scheme like 64-QAM, the bandwidth needs to be  $\sim 800$  MHz [48]. This implies that the switching speed of the DC-DC converter in the ET needs to be  $\sim 1.5$  GHz (2  $\sim 3 \times$  bandwidth). To worsen the situation, in a typical high efficiency hybrid ET, the DC-DC converter already constitutes the bottleneck in the bandwidth [49]. The use of existing GaN n-FETs in the high side switching of the power converter requires a level shifter which results in a degradation of the bandwidth. Alternatively, Si p-FETs may be used, but at the expense of lower voltage rating and higher switching. Therefore, the development of a high performance wide band gap p-channel high-side switch, such as a GaN p-FET, is required to widen the bandwidth of ETs.

GaN-CMOS technology, if successful, would be a fundamental device-level advancement that could bring about advancements in the RF front end. A simplified schematic of the RF transmitter, consisting of the power amplifier, is illustrated in Fig. 1.1(a). Specifically, two areas are discussed:

1. GaN CMOS DC-DC converter for use in hybrid ET: The use of a GaN p-FET switch is proposed for a wide bandwidth dynamic power supply to be used in 5G PAs (Fig. 1.1(a)). In the

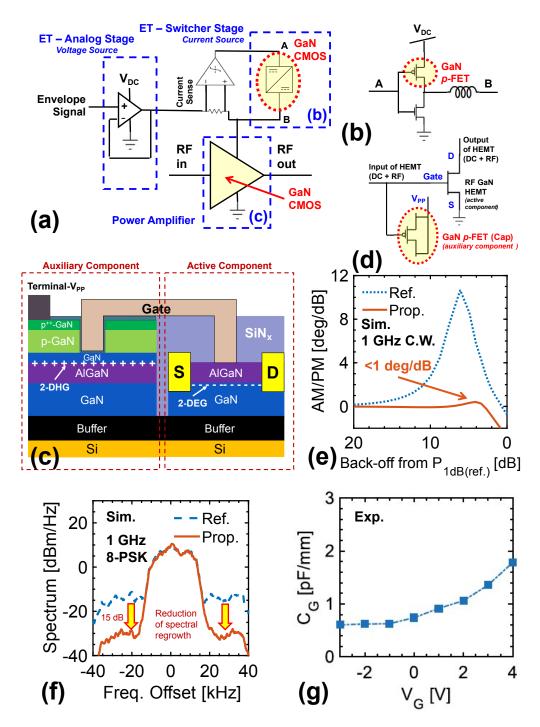

Figure 1.1: Applications of GaN-CMOS technology in the RF front end. (a) Schematic of the RF transmitter. The proposed novel components based on GaN-CMOS technology are highlighted. (b) Circuit diagram of the proposed DC-DC converter used in the switcher stage of the ET. (c) Proposed integrated GaN-CMOS device to achieve higher linearity. (d) Simplified circuit model of the proposed linearized device used in the simulations. Proof-of-concept simulations indicate promising performance: (e) One-tone load-pull at 1 GHz, showing significant reduction in AM/PM to < 1.5 deg/dB. (f) 1 GHz 8-PSK operation, showing reduction in spectral regrowth. Significant improvement in EVM (by > 60 %) at higher receiving channel powers was observed. (g) Preliminary experimental results of a linearized capacitance profile of a GaN n-FET with  $V_{th} = 2$  V and ON-OFF ratio of  $10^8$ .

switcher stage (Fig. 1.1(b)), the GaN p-FET would be gated by pulses from the analog stage. Here, no level shifters are required because the high-side switching is performed by the p-FET. Therefore, assuming p-FETs with high switching performance are deployed, GaN-CMOS technology is expected to realize wide bandwidth envelope trackers in the power management ICs.

2. Linear GaN amplifier using "capacitance compensation": An integrated device which could offer higher linearity has been designed based on the GaN CMOS platform (Fig. 1.1(c)). Extensive proof-of-concept simulations (Fig. 1.1(d)) reveal that, the linearized device yields significant improvement in linearity (Fig. 1.1(e)–(f)) [12]. In addition, preliminary experimental results reveal linearized gate capacitance for a RF n-FET (Fig. 1.1(g)), attesting to the feasibility of the proposed concept. While existing demonstrations of the proposed GaN CMOS platform have been on GaN-on-Si wafers, the technology could be easily transferred to GaN-on-SiC wafers to provide optimal environment for maximum microwave power performance.

### **1.2 Early Work on GaN-CMOS**

As a disclaimer, here (and throughout the thesis), the term "GaN-CMOS" refers to the concept of complementary GaN-based transistors (GaN-based p-FET and GaN-based n-FET), similar to the Si-CMOS technology (Si-PMOS and Si-NMOS FETs) prevalent today. The concept may be further extended to complementary transistors based on other III-N materials. In the case of specific transistor structures, the term "complementary transistors" or "complementary technology" (CT) will be used instead, because "CMOS" contains references to the MOS (metal-oxidesemiconductor) structure. "GaN-CMOS" does not typically require a carrier inversion layer as is the case in more conventional Si-CMOS. In this thesis, unless otherwise stated, "complementary transistors" does not refer to the novel device architecture "complementary transistor (CFET)" proposed for Si advanced logic nodes, though GaN-CFET would be a promising area for future work [50].

Pioneering experiments have been conducted in the area of GaN-CMOS. Most experiments have focused on demonstrating p-FETs (which is the missing piece of the puzzle in a GaN-CMOS technology), while some significant works of GaN-CMOS by Chu, Hahn, Nakajima, Chowdhury, Zheng *et al.* [11,26,27,51,52] have demonstrated integrated GaN complementary transistors and/or circuits. In recent years, this rapidly advancing field has witnessed the demonstrations of: (1) complex complementary circuits [53]; (2) high performance p-FETs using (i) various epitaxial structures [54–57,57–59], (ii) novel transistor architectures (e.g. FinFET [58,60–63]), and (iii) process technologies [53,64–67]. Thus far, discrete III-N p-FETs have received significant attention, but equal attention should be paid to their monolithic integration with n-FETs.

Broadly speaking, there are two categories of GaN-CMOS platforms. First is the epitaxial regrowth approach, where the n-channel and p-channel are formed separately. In the experiment of Chu et al. (2016), the as-grown epitaxy consists of AlGaN (for n-channel). Then, after some fabrication steps, the p-GaN is regrown and patterned in selective regions (where the p-FET will be located). The second category, which is more prevalent in the literature, is the co-existence of n-channel and p-channel on the same epitaxy, typically by as-grown p-GaN/AlGaN/GaN (or variant). There are advantages and disadvantages of each approach. The first approach allows for independent optimization of the n-channel and p-channel separately, but regrowth of p-GaN is costly, and requires careful processing. Much optimization would be required to ensure high quality of the regrown p-GaN (and the interface with AlGaN), compared to conventional as-grown p-GaN (in-situ with AlGaN/GaN). The second approach allows for the easy integration of n-FET and p-FET, by designing transistor structures which make use of each channel. The challenge is that the properties of the n-channel and p-channel (therefore, n-FET and p-FET) are inevitably coupled because both channels rely on the *same* AlGaN layer as the polarization-inducing layer. Therefore, for such structures, the challenge in integration is more than just the fabrication. At this stage, basic integration of n-FET and p-FET has been demonstrated in several early works cited above. Two major challenges need to be addressed for such integrated GaN-CMOS platforms: (1)

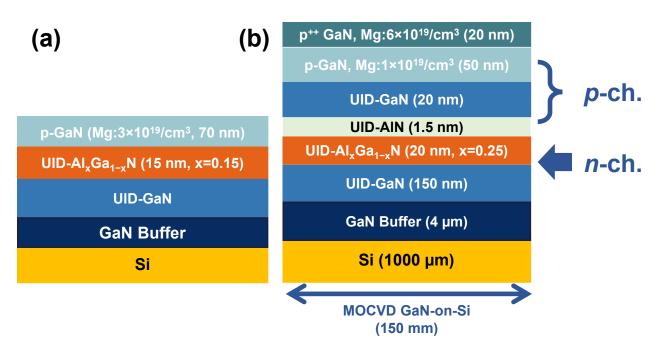

Figure 1.2: GaN-CMOS platform. (a) A conventional epitaxy for p-GaN-gate power HEMT, for illustrative purpose. (b) Epitaxial structure of the GaN-CMOS platform used in this thesis. Note that all doping levels are nominal values provided by the supplier. Actual doping profile is affected by non-idealities such as the Mg doping delay and memory effect.

how to ensure high performance transistors in *both* n-FET and p-FET, (2) how epitaxial features introduced for one type of transistor would affect the performance of the other type of transistor. These challenges will be taken into full consideration in this thesis.

### **1.3 GaN-CMOS Platform Used in This Thesis**

Before introducing the GaN-CMOS platform, it is insightful to review the conventional p-GaN platform, typically used for power HEMTs. A typical epitaxy is shown in Fig. 1.2(a). At the top of the conventional AlGaN/GaN epitaxy (used for E-mode HEMTs), a p-GaN layer is added to ensure normally-off operation, by depleting the 2DEG channel (AlGaN/GaN interface) at zero bias conditions.

The GaN-CMOS platform used in this work is inspired by the conventional p-GaN platform, but contains several notable differences. As presented in Fig. 1.2, the GaN-CMOS platform consists of  $p^{++}$ -GaN, p-GaN, GaN, AlN, AlGaN and GaN layers (unintentionally doped (UID) if

doping is not specified). The  $p^{++}$  layer (with a high doping level of  $6 \times 10^{19}$  cm<sup>-3</sup>) would benefit the formation of ohmic contacts to p-GaN. Another feature is the insertion of UID-GaN, which seeks to reduce carrier scattering in the GaN/AlGaN interface (due to significantly less doping). It could be thought of as a "spatial separation" of the dopant from the quantum well, which is a feature that gives the high mobility of electrons in GaAs pHEMTs.

The GaN-CMOS platform features the co-existence of the p-channel and n-channel. The pchannel consists of the p-GaN (bulk channel) and the 2DHG channel at the GaN/AlGaN interface, a property of this epitaxy which will have profound implications in the p-FET characteristics (refer to Chapter 4). The n-channel is formed by the AlGaN/GaN 2DEG, which is depleted at zero bias. While the epitaxy could be grown in a variety of substrates (e.g. SiC, sapphire, Si, AlN), in this work, the Si (111) substrate is used due to the scalability (large diameter wafers, a desired property of GaN-CMOS technology, refer to Chapter 1.4) and low cost. For similar reasons, MOCVD is used (instead of MBE), despite several advantages of MBE (e.g., maximum p-GaN doping could be higher in MBE [68]).

### 1.4 Requirements of Next-Generation GaN-CMOS Technology

While early experiments have indicated the feasibility of GaN-CMOS, further advancements in several aspects of this technology are needed to realize the proposed circuit-level applications. In fact, based on the GaN-CMOS platform of this work (Fig. 1.2(b), less AlN layer), significant progress has been made in the performance of p-FETs [61, 65, 69, 70]. Therefore, the question is, how could we push GaN-CMOS technology further to make it a reality?

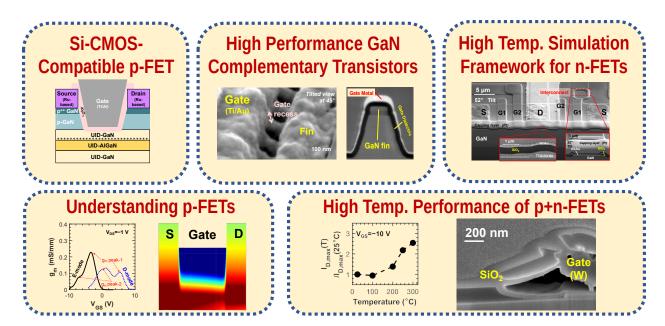

At this stage of GaN-CMOS research, this thesis advocates an application-driven perspective to the issue of advancing GaN-CMOS platform. Fig. 1.3 lists various requirements (of the GaN-CMOS technology as a whole) and the proposed solutions adopted in this thesis.

1. Easy integration of n-FET and p-FET. As mentioned earlier in this chapter, a major advantage of the p-GaN/AlGaN/GaN epitaxy (or variants) is the co-existence of both n-channel

Figure 1.3: Advancing next-generation GaN-CMOS technology through an application-driven perspective. The requirements of the technology and the proposed solutions (adopted in this thesis) are indicated.

and p-channel on the same epitaxial structure. This serves as the basis for the easy integration. This avoids the need for costly regrowth steps. In earlier work, a regrowth-free GaN complementary circuit (logic inverter) was demonstrated, therefore proving the feasibility of the GaN-CMOS platform for easy integration [26]. Later, experiments of similar integration on similar epitaxial structures have been reported by other researchers (Chapter 1.2), therefore attesting that the integration results are reproducible. This thesis builds upon this capability where n-FETs and p-FETs are monolithically integrated.

2. Scalability of the wafer platform. MOCVD GaN-on-Si were epitaxially grown by commercial suppliers on 150 mm and 200 mm Si (111) wafers. The use of larger diameter wafers is in line with industry trends (e.g. 300 mm reported by Intel Corp. [45]) and also benefits from the sophistication of processing equipment (designed for larger diameter wafers). Scalability and MOCVD growth (significantly higher throughput than MBE) are major considerations for the commercialization of GaN electronics; the vast majority of the commercially available GaN electronics are grown by MOCVD.

- 3. High performance p-FET and n-FET. The need for high performance transistors is a central requirement of any technology, especially in GaN-CMOS which is an emerging concept. Furthermore, considering Requirement 1, it was decided from the start that such high performance complementary transistors need to be based on the same GaN-CMOS platform, so as to attract IC designers to adopt the technology. The high performance p-FETs are only as impactful as they can be, *if and only if* they can be properly integrated with n-FETs for IC applications. In this thesis, the approaches to achieving higher performance are device innovation and process optimization. Emphasis is placed on the demonstrations of *novel* (as opposed to solely optimized) device features and process (e.g., self-alignment in p-FET and n-FET gate).

- 4. Si-CMOS-compatible metallization. In the early demonstrations of GaN HEMTs and p-FETs, a gold-based process was used, which precludes them from being fabricated in Si-CMOS-compatible foundries. Si-CMOS-compatibility is mutually beneficial for both GaN-CMOS technology and the foundries on one hand, such a technology would be more readily uptaken by the foundries, therefore increasing the impact of the GaN-CMOS technology; on the other hand, GaN-CMOS technology could benefit from the sophisticated process capability in Si foundries to greatly improve on the process stability and quality for GaN-CMOS technology. This work explores the use of Ru-based S/D contacts, and demonstrates their integration in p-FETs.

- 5. High temperature operation. The characterization of complementary transistors under HT stress is desired to ensure: (1) HT operation for a variety of industrial applications (e.g. automotive), (2) reliable operation at high power, (3) reduced cooling and thermal management needs, and (4) harsh environment electronics (e.g. for hypersonic aircraft and outer space exploration). While there are some early characterization of GaN p-FETs at HT, with the rapid advancements in the field, it is important to characterize the latest p-FETs. Furthermore, the p-FETs based on the GaN-CMOS platform (addition of UID-GaN) shows a distinct behavior

at HT, as compared to p-FETs based on a conventional p-GaN/AlGaN/GaN platform. For n-FETs, given that their temperature-dependent characteristics are well studied, the characterization under realistic extreme environment conditions is the natural next step.

Requirements 1–2 have been addressed in early works, in which the author has made substantial contributions. Considering the above, this thesis focuses on innovative solutions for requirements 3–5. In this way, this thesis aims to make fundamental contributions to the vision of next-generation GaN-CMOS technology and its adoption.

## 1.5 Objectives and Methodology

The objectives and methodology of the thesis are as follows:

- 1. To advance GaN complementary transistor technology through exploring the scaling limits of such transistors.

- 2. To explore the potential of the proposed GaN complementary transistors (especially p-FET) for commercialization, through Si-CMOS-compatible metallization.

- 3. To understand the unique transistor characteristics of p-FETs through a combination of measurements and TCAD simulation/modeling.

- 4. To develop a device-to-circuit level simulation framework to aid the scaling-up of transistor/basic circuits on the p-GaN platform.

- 5. To study the high temperature performance of GaN complementary transistors, and the harsh environment robustness/degradation of p-GaN-gate HEMTs (n-FETs).

### **1.6 Organization of the Thesis**

This thesis, with the central theme of advancing GaN complementary transistors and circuits based on a p-GaN platform, is organized as follows. Chapter 2 "Highly Scaled GaN Complementary Technology" presents the pursuit of high performance in complementary GaN transistors (p-FET and n-FET) based on the GaN-CMOS platform. Through aggressive scaling in the channel length and fin width dimensions, and the use of self-aligned features, highly scaled p-FETs (self-aligned-gate p-FETs) and n-FETs (self-aligned W/p-GaN gate HEMT) with record performance are demonstrated. The trends of scaling are studied. An improved ICP-RIE p-GaN/AlGaN selective etch is developed.

Chapter 3 "Si-CMOS-Compatible GaN p-FET" addresses another major roadblock towards the commercialization of GaN-CMOS technology, which is the (lack of) Si-CMOS-compatible metallization. A Ru-based S/D-contact technology was developed and optimized. Ru-based S/D contacts are integrated into a self-aligned p-FET (ohmic-first) process. A novel gate recess technology was developed for E-mode p-FETs.

Chapter 4 "Unique Design Space of GaN p-FETs" seeks to deepen the understanding of the state-of-the-art p-FETs based on the GaN-CMOS platform. The impact of gate recess on the transfer characteristics of the p-FET is analyzed through TCAD simulation, which was later verified by experiment. TCAD simulation indicates the existence of the two components of the channel, and their contributions to the transistor characteristics. Furthermore, the impact of a realistic p-doping profile (as opposed the idealized uniform doping) is studied and reveals trade-offs in the p-FET characteristics.

Chapter 5 "p-FETs and n-FETs for High Temperature Operation" examines the HT performance of the p-FET and n-FET. A novel p-FET (with Ru-based S/D, described in Chapter 3) was measured at HT up to 300 °C. The DC characteristics are analyzed. Newly developed understanding from Chapter 4 is used to explain the unique HT behavior of the p-FET. The characterizations of n-FET (p-GaN-gate HEMT) at HT and after harsh environment exposure are briefly discussed. The concept of a p-channel junction FET (JFET) is proposed to achieve HT robust p-FETs, and preliminary process development is conducted for the short-channel p-n junction gate.

Chapter 6 "Towards DTCO in high temperature GaN-on-Si technology: a CAD framework up to 500 °C" presents a device-to-circuit simulation framework for novel GaN electronics, using the

case study of n-FET-based GaN HT electronics. Through detailed characterization of the transistors and circuits at HT up to 500 °C, models are established and verified at the circuit-level. This work serves as a stepping stone for the eventual DTCO of GaN n-FET-based HT electronics, and also a future simulation framework for GaN-CMOS technology.

Chapter 7 "Conclusion and Future Work" summarizes the work and proposes several areas of future work, ranging from the device (transistor)-level, to circuit-level (proof-of-concept circuit demonstrations of GaN-CMOS), and the need for a robust simulation framework.

# Chapter 2

# Highly Scaled GaN Complementary Technology

The materials in this chapter are partially based on the following publications. The published materials in the publications mentioned below are reused with permission.

Q. Xie *et al.*, "Highly-Scaled Self-Aligned GaN Complementary Technology on a GaN-on-Si Platform," 2022 International Electron Devices Meeting, pp. 35.3.1–35.3.4, Dec. 2022. © 2022 IEEE [71]

Q. Xie *et al.*, "Highly Scaled GaN Complementary Technology on a Silicon Substrate," *IEEE Transactions on Electron Devices*, vol. 70, no. 4, pp. 2121–2128, Apr. 2023. [72]

### 2.1 Introduction

As discussed in Chapter 1.2, several recent works have studied the feasibility of a GaN complementary technology (CT). In view of the above application requirements and among the various options, the GaN CT platform in [26] based on p-GaN/UID-GaN/AlGaN/GaN heterostructure stands out as a promising candidate. This work seeks to advance the performance of GaN p-FET and n-FETs on this platform, through a combination of device innovation and process optimization. A distinctive feature of these transistors is the aggressive scaling in the p-FET and n-FET, including self-aligned (SA) gate etch. It is noted that, aggressive scaling has been adopted in a wide range of novel transistors to improve their performance [17, 73], and will be a key strategy pursued in this work.

The organization of this chapter is as follows. The concepts of the p-FET and n-FET are explained in Chapter 2.2. The fabrication and characterization of the p-FET are presented in Chapter 2.3, followed by the same aspects of the n-FET in Chapter 2.4. Chapter 2.5 presents a benchmarking of the proposed GaN CT and an overview of the areas of future research, followed by Chapter 2.7 which concludes the article.

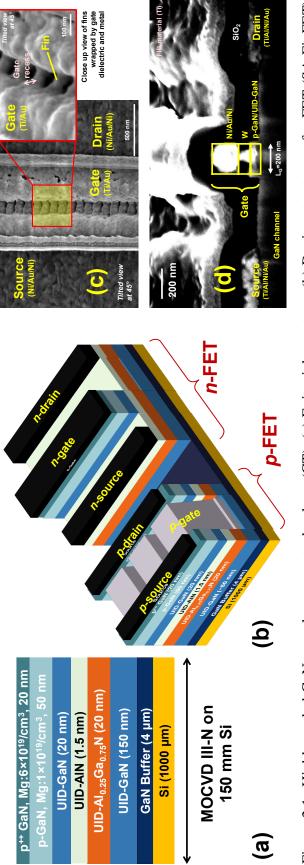

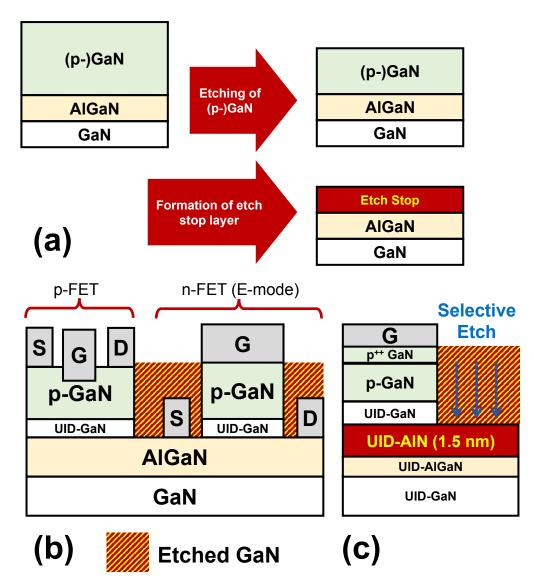

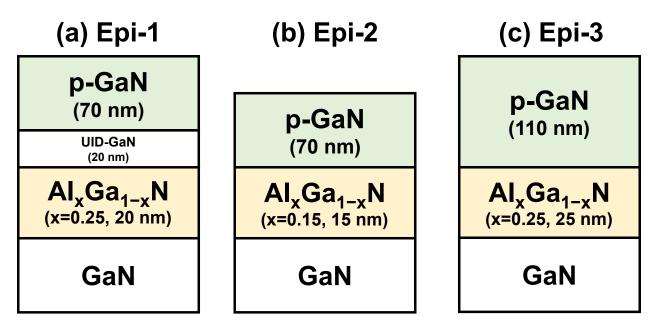

# 2.2 Epitaxial Platform and Transistor Architectures of GaN CT

The starting material is the GaN-CMOS platform as shown in Fig. 1.2(b). The epitaxial structure ("Epi-1", Fig. 2.1(a)) is modified from earlier work [26] by inserting a 1.5 nm AlN (in actual implementation, high Al composition AlGaN) layer. The use of an AlN layer allows for polarization enhancement of the p-channel charge density [55] and a better etch stop during the selective etch of p-GaN/UID-GaN over AlGaN (a key process step for the n-FET). Both p-FETs and n-FETs were fabricated on this structure (Fig. 2.1(b)–(d)). The same epitaxial structure of Fig. 2.1(a) was processed to realize the p-FET and n-FET (Fig. 2.1(b)). In this chapter, unless otherwise stated, the p-FET and n-FET refers to GaN-based transistors.

The transistor architecture of the p-FET is the FinFET which features self-alignment between the ohmic and gate. A representative p-FET is shown in Fig. 2.1(c). Channel length scaling of p-FETs is critical to overcome the low hole mobility in these transistors (experimentally measured to be typically  $< 30 \text{ cm}^2/\text{V} \cdot \text{s}$ ) and to take advantage of field-induced acceptor ionization [69, 70]. To this end, a SA FinFET architecture [61] was adopted in this work as it offers new opportunities for p-FET design. The impact of fin width scaling and recess depth on these transistors was studied. Further improvement in transistor performance was also contributed by optimizations to the key process steps of the proposed p-FET, which will be described in Section 2.3.1.

This work also seeks to improve the performance of GaN n-FETs based on the GaN CT platform through the development of a gate technology where the gate metal is self-aligned (SA) to the p-GaN region. The realization of E-mode n-FETs is highly desired for a wide variety of applications, including power electronics, as well as digital and RF integrated circuits (ICs), where the bias circuitry could be simplified by eliminating the need of a third bias terminal ( $V_{SS}$ ) [74]. Recent efforts have also explored the potential of such short-channel p-GaN-gate HEMTs for RF applications, including in PA and LNA [75, 76].

Approaches to the realization of GaN E-mode n-FETs include, F-plasma treatment of gate region [77], MIS-recessed gate [78], FinFET/tri-gate [79] and p-GaN-gate [26]. In this work, the p-GaN-gate n-FET is chosen because (1) easy integration with p-FET (Fig. 2.1(b)) and other power IC components [8]; (2) minimum degradation of as-grown gate surface (i.e. no photo-resist or etching), which reduces hysteresis and trapping issues; (3) demonstrated performance and robustness in GaN circuits at high temperature (up to 500 °C) [80, 81].

While numerous p-GaN-gate HEMTs have been reported in the literature, the introduction of self-alignment between the metal electrode and the p-GaN would be beneficial for: (1) achieving a shorter p-GaN gate length, because the alignment tolerances needed for the metallization would not be applicable; (2) reduction of gate capacitance, which is key for high-speed low/medium-voltage power ICs and analog mixed-signal applications.

The planar architecture was chosen for the n-FET (p-GaN-gate HEMTs). A representative p-FET is shown in Fig. 2.1(d). The choice of the planar architecture is not just due to process simplicity, but also due to other considerations. Most conventional power HEMTs rely on the planar architecture and excellent performance has been obtained. Furthermore, looking at GaN-CMOS holistically, the key performance improvement needs to originate from the p-FET (with respect to the n-FET). The key for n-FET is to ensure that competitive performance is maintained.

(As will be shown in Chapter 2.5, the n-FET of this work also achieves competitive performance.) Having said that, there are demonstrations of E-mode FinFETs (tri-gate) based on the p-GaN-gate structure [82]. If the FinFET (tri-gate) concept were to be adopted for the E-mode n-FET, the range of device designs would not just be limited to p-GaN-gate FinFETs, but also junction tri-gate FETs using NiO and LiNiO [83, 84].

### 2.3 GaN p-FET

#### 2.3.1 Self-Aligned GaN p-FinFET Process Flow

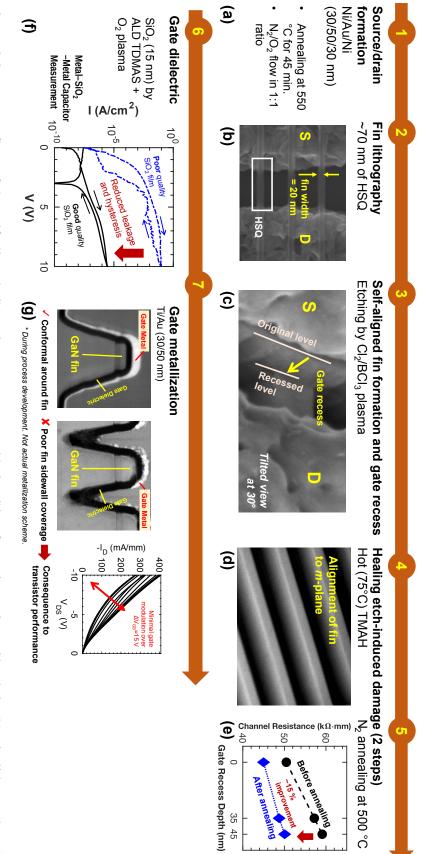

The process flow of the p-FET is an optimized version of the baseline flow as reported in [61], and is illustrated in Fig. 2.2. Here, the entire flow is described in detail, with the key improvements highlighted to showcase the novelty of this work. The flow begins with the S/D metallization using Ni/Au/Ni (30/50/30 nm) deposited by electron beam evaporation and patterned by a lift-off technique. Then, the S/D metal is alloyed at 550 °C for 45 min. in N<sub>2</sub>/O<sub>2</sub> (1 : 1 ratio). The annealing of Ni/Au in O<sub>2</sub> allows for the formation of Ga vacancies in the p-GaN (through Ga-Au alloy), and the formation of NiO<sub>x</sub> which has high workfunction to p-GaN [85, 86].

Next, the fin lithography is performed using 4% hydrogen silsesquioxane (HSQ), which results in a ~ 70 nm layer of HSQ. A fin width of 20 nm is achieved here. Next, the fins are patterned through etching by BCl<sub>3</sub>/SF<sub>6</sub> plasma and SiO<sub>2</sub> (formerly HSQ) as mask. Note that the fins extend from the source to the drain. The fins were aligned to the *m*-plane, in order to ensure smooth sidewalls as discussed later [87]. The SiO<sub>2</sub> (formerly HSQ) on the fins is removed using a quick (~ 2 min.) buffered oxide etch (BOE 7 : 1) dip. Then, a SA gate recess (SA to the S/D) is conducted using the same Cl<sub>2</sub>/BCl<sub>3</sub> plasma RIE recipe as above. A time-controlled etch is used. A mediumpower BCl<sub>3</sub>/SF<sub>6</sub>-RIE (etch rate of ~ 1 nm/min.) was used for these steps as a compromise among damage to ohmic contact, fin etch-induced damage, and good etch geometric profile. The optimized process was capable of achieving fin widths of 20 nm at  $L_{SD}$  of < 200 nm. The SA architecture ensures that the access region (and access resistance) is negligible and that the entire

and n-FET (SA-gate p-GaN-gate HEMT) based on the same GaN-on-Si platform as illustrated in Fig. 2.1(a). (c), (d) Scanning electron Figure 2.1: Highly-scaled GaN complementary technology (CT). (a) Epitaxial structure. (b) Device structures of p-FET (SA FinFET) microscopy (SEM) images of representative p-FET and n-FET, respectively.

gate control, especially for closely packed fins. observed. (f) Atomic layer deposition (ALD) of gate dielectric (SiO<sub>2</sub>). Typical characteristics of metal-insulator-metal (MIM) capacitors etch-induced damage (step 2),  $N_2$  annealing at 500 °C for 1 h.  $\sim 15$  % improvement in the channel resistance for various recess depths is (with variation in quality of  $SiO_2$  films) is presented. (g) Gate metallization. Conformal gate metallization is extremely important for mask. (d) Healing etch-induced damage (step 1), tetramethylammonium hydroxide (TMAH) treatment at 75 °C for 5 min. (e) Healing (formerly HSQ) as mask, which ensures self-alignment to S/D contacts, (2) after removal of SiO<sub>2</sub>, SA gate recess using S/D contacts as aligned to the m-plane. (c) SA gate region. Two etches were conducted using medium-power  $Cl_2/BCl_3$  plasma, (1) fin etch, using SiO<sub>2</sub> improved fin lithography process using thinner HSQ (70 nm) has allowed for aggressive scaling of the fins down to 20 nm fin width. Figure 2.2: Process flow of the self-aligned (SA) FinFET: (a) source/drain (S/D) formation using Ni/Au/Ni. (b) Fin lithography. An The HSQ thickness was carefully calibrated to achieve a balance between fine lithography and subsequent etch resistance. Fins were

length of the fin (=  $L_{SD}$ ) is gated. Otherwise, an access region with the fin architecture would greatly increase the access resistance (normalized by total width, taking fin pitch into account), and would nullify the positive impact of channel length scaling in these p-FinFETs.

When compared to a planar channel, the fin channel has more surface area exposed to RIE plasma. Therefore, several steps were conducted to heal etch damage. Two steps are used to heal the etching damage, namely the tetramethylammonium hydroxide (TMAH) treatment at 75 °C for 5 min., which ensures the smoothness of the m-plane sidewalls, and N<sub>2</sub> annealing at 500 °C for 1 h.  $\sim 15$  % improvement in the channel resistance for various recess depths is observed. Then, atomic layer deposition (ALD) of gate dielectric (SiO<sub>2</sub>) is conducted using tris(dimethylamino)silane (TDMAS) precursor and O<sub>2</sub> plasma at 250 °C. Typical characteristics of metal-insulator-metal (MIM) capacitors (with variation in quality of SiO<sub>2</sub> films) is presented. For a representative MIM capacitor fabricated with a good quality film, low hysteresis (< 1 V) and leakage (< 1  $\mu$ A/cm<sup>2</sup>) (at 5 V) could be obtained. To the contrary, for a representative MIM capacitors fabricated with a poor quality film, high leakage  $\sim 10$  mA/cm<sup>2</sup>) is observed, together with highly fluctuating I-V measurement. In the worst case, such films are permanently degraded after a few repeated measurements. The gate dielectric quality and p-GaN/dielectric interface make a significant contribution to the device switching characteristics, therefore making this an area of active research [88,89].

The last step is the gate metallization, which is done by a sputtering and lift-off process. Conformal gate metallization is extremely important for gate control, especially for closely packed fins. Through various experiments and cross-section microscopy, it was observed that, for such GaN p-FinFET gate structures, the fin packing factor (pitch between fins) and the slope of the sidewall are key factors. Fig. 2.2(g) gives two examples of gate metallization. For poor gate metallization, typically the p-FinFET could not turn off even for a very deep gate recesses (little p-GaN/UID-GaN remaining above AlGaN). RF magnetron sputtering of Ti/Au (30/50 nm) was used. Ti was chosen because of its low workfunction (therefore Schottky to p-GaN), and its good adhesion to the SiO<sub>2</sub> surface. Unfortunately, the gate metal could not be too thick because a lift-off technique was used for sputtered metal. A MMA/PMMA layer was used to create a huge undercut (larger than bi-layer PMMA) which would be advantageous for the lift-off. A detailed description of the process flow is provided in Appendix A.

### 2.3.2 Results and Discussion

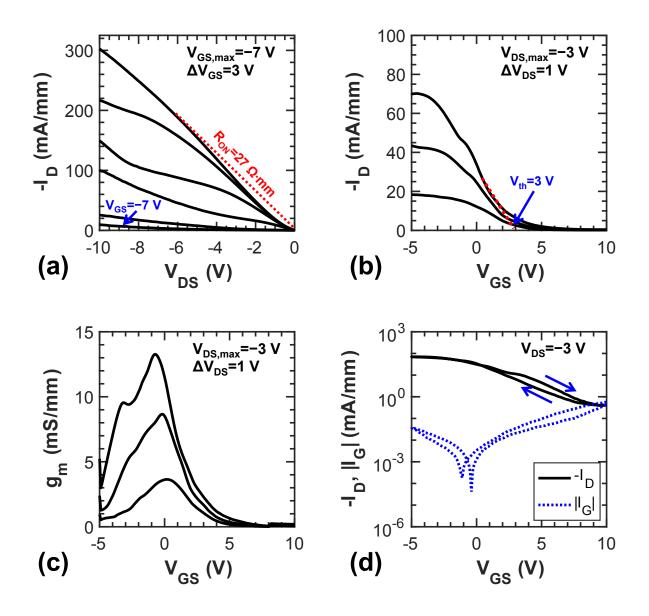

The performance of the p-FET with the best overall characteristics ( $L_{SD} = 175$  nm,  $L_G$  self-aligned, fin width of 20 nm) is presented in Fig. 2.3. An  $I_{D,max}$  of -300 mA/mm,  $R_{ON}$  of 27  $\Omega$ ·mm, and current saturation at high gate overdrive were achieved, as shown in Fig. 2.3(a). The transfer characteristics (Fig. 2.3(b)) reveal a  $V_{th}$  of 3 V and a peak transconductance,  $g_m$ , of 13 mS/mm. A second  $g_m$  peak at large gate overdrive and highly negative  $V_{DS}$  likely indicates a second channel being activated, and is investigated in Chapter 4.1. The drain current ON/OFF ratio is 200, limited by the leakage current through the gate dielectric. The hysteresis in the transistor transfer characteristics ( $\sim 1$  V) resembles the hysteresis in metal-SiO<sub>2</sub>-metal capacitors (Fig. 2.2(f)), which indicates the significant contribution of the gate dielectric quality (and p-GaN/dielectric interface) and need for further optimization.

The impact of two key device design parameters (fin width, gate recess depth) on DC output characteristics ( $I_{D,max}$ ,  $R_{ON}$ ) was systematically studied for GaN p-FinFETs. As the fin width is reduced below 50 nm, the current density and  $R_{ON}$  improves (Fig. 2.4(a)). However, this trend was not observed above 50 nm, possibly due to the significant reduction in the field-induced acceptor ionization effect [70]. In addition, a deeper gate recess was found to reduce current density (Fig. 2.4(b)), primarily due to reduction of carrier density in the p-channel, but is expected to significantly improve ON-OFF ratio and sub-threshold swing, as is the case for p-FETs based on similar epitaxial structures. Unfortunately, the gate oxide quality in this batch of fabricated transistors was found to be the limiting factor for the current ON-OFF ratio (< 10<sup>4</sup>). It follows that, the OFF-state characteristics were limited by gate control and drain-induced barrier lowering (DIBL), before a destructive breakdown at ~ 20 V.

Figure 2.3: Performance of p-FET with  $L_{SD} = 175$  nm ( $L_G$  self-aligned), fin width= 20 nm. (a) Output characteristics, showing  $I_{D,max} = -300$  mA/mm,  $R_{ON} = 27 \ \Omega \cdot mm$ . Current saturation at higher gate overdrive was observed. Transfer characteristics: (b) Linear  $I_D vs$ .  $V_{GS}$ , showing  $V_{th} = 3$ V. (c) Transconductance vs.  $V_{GS}$ , showing peak  $g_m = 13$  mS/mm ( $V_{DS} = -3$  V). (d) Logarithmic  $I_D vs. V_{GS}$ . Current ON/OFF ratio is 200, limited by the gate leakage. The hysteresis is typically attributed to the interface traps at the gate oxide.

Figure 2.4: Systematic study of the impact of (a) fin width and (b) gate recess depth on the performance  $(-I_{D,max} \text{ and } R_{ON})$  of GaN p-FinFETs. SA p-FinFETs (~40 in total) fabricated in the same batch.  $-I_{D,max}$  and  $R_{ON}$  were measured at  $V_{GS} = -7$  V.

## 2.4 GaN n-FET

## 2.4.1 Self-Aligned p-GaN-Gate HEMT Process Flow

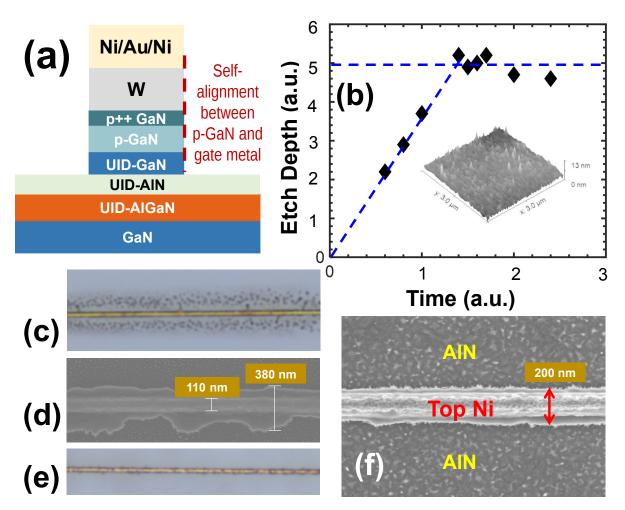

Self-aligned p-GaN-gate technologies were previously explored [90, 91]. This work proposes a simple gate-first process flow, which incorporates novel (1) metallization scheme with lower sheet resistance, (2) GaN/AlGaN selective etch recipe, (3) etch hard mask to ensure aggressive scaling of the gate length.

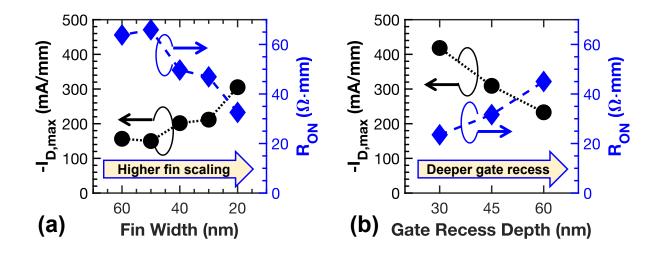

As illustrated in Fig. 2.5, the SA gate process begins with the blank sputtering deposition of W (100 nm). Then, Ni/Au/Ni (30/120/80 nm) was patterned by electron beam lithography and lift-off. W was etched using the top Ni as a hard mask. W was chosen because of its high thermal stability (necessary for a gate-first process) and Schottky behavior with p-GaN gates [65]. p-GaN and UID-GaN (above AlGaN) were etched using SF<sub>6</sub>/BCl<sub>3</sub>. The optimization of the epitaxy and selective etch will be explained next. Lastly, ohmic contacts were formed by Ti/Al/Ni/Au alloyed at 800 °C in N<sub>2</sub> ambient. The typical contact resistance is ~ 0.75  $\Omega$ ·mm, which could be further optimized for contact formation through the AlN/AlGaN barrier. A fabricated scaled

### Gate metallization

#### Self-aligned p-GaN-gate formation

Figure 2.5: Process flow of self-aligned W/p-GaN-gate n-FET: (a) Conformal deposition of W, then patterning of Ni/Au/Ni (30/120/80 nm) using electron beam lithography and lift-off. (b) Self-aligned (SA) p-GaN gate formation is achieved using reactive ion etching (RIE) of W and GaN (recipes are included). AlN layer aids the etch stop to minimize damage to the n-channel. (c) Formation of ohmic contacts using alloyed Ti/Al/Ni/Au. (d) TLM measurement of ohmic contacts. In the SA p-GaN-gate, the extent of the p-GaN region is defined by the top Ni/Au/Ni.

SA p-GaN-gated n-FET is presented in Fig. 2.1(d). A detailed description of the process flow is provided in Appendix A. A proof-of-concept layout was adopted, where the fabricated n-FETs are symmetric (gate is located in the center of the ohmic contacts, or  $L_{GS} = L_{GD}$ ), and that electric field management structures (e.g. edge termination) were not included.

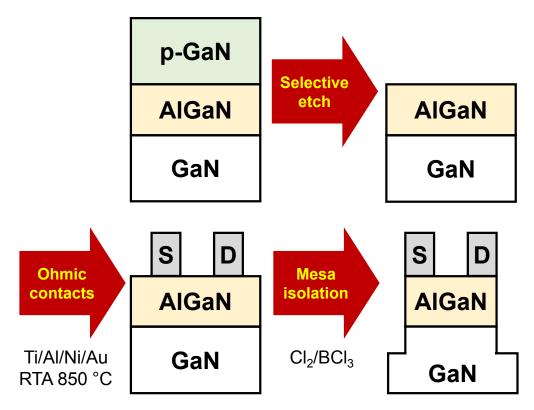

It is evident that an important step for the p-GaN HEMT is the selective etch, where the p-GaN is selectively removed over AlGaN, or in other words, the etch stops at the AlGaN layer. This step is in between the steps in Fig. 2.5(a)–(b). The purpose is to completely remove the p-GaN in the ohmic regions (for formation of ohmic contact to AlGaN/GaN 2DEG) and in the access regions (to recover the 2DEG from the depletion by p-GaN). Any remaining p-GaN (incomplete etch) would lead to an increase in access resistance or the poor performance of ohmic contacts. Furthermore, if a conventional Cl-based etch for III-N were to be used, the etch has little selectivity between GaN and AlGaN, therefore the etch would need to be perfectly timed to ensure the etch stops on AlGaN. Such a recipe requires very careful calibration of the etch rate, and more importantly, is not robust to variations in p-GaN thickness across the sample, variation in local etch rate across the sample etc. Instead, the selective etch relies on achieving an "etch stop" layer at the AlGaN top surface.

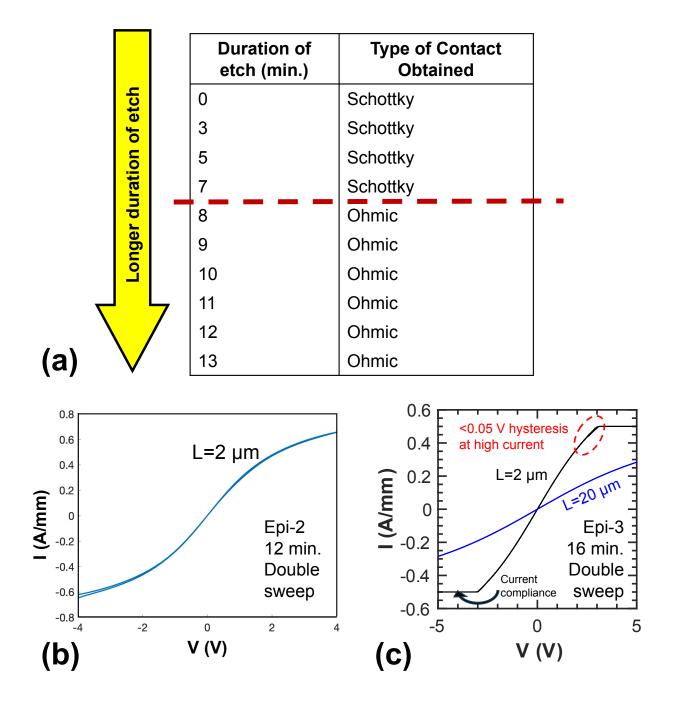

Fig. 2.6(a) explains the concept of a selective etch, from a fabrication perspective. The etch chemistry needs to be able to etch GaN, but effectively form an "etch stop" layer. In this work,  $BCl_3/SF_6$  plasma was used, which has been reported to give high etch selectivity [92]. To the first order,  $BCl_3$  etches GaN, while  $SF_6$  allows for the formation of non-volatile  $AlF_x$  (not possible during etching of GaN). Selective etching of p-GaN over AlGaN was achieved using  $BCl_3/SF_6$  plasma, which has been reported to give high etch selectivity [92].

In the former GaN-CMOS platform, the selective etch would resemble the schematic shown in Fig. 2.6(b), where the shaded region denotes the etched p-GaN/UID-GaN through the selective etch process. In order to achieve a better etch stop at the AlGaN layer, a UID-AlN layer (in actual implementation in MOCVD,  $Al_xGa_{1-x}N$  with x > 0.8 layer is inserted in the GaN-CMOS epitaxy of this work. In the case of the selective etch recipe used, the F (from plasma) forms a nonvolative AlF<sub>x</sub> layer, therefore effectively creating an etch stop. An AlGaN layer with a higher Al

Figure 2.6: Selective etch for fabrication of n-FET. (a) Schematic of GaN-CMOS platform (former epitaxy) with p-FET and n-FET, showing the selectively etched p-GaN/UID-GaN region. (b) Epitaxy of this work which incorporates a UID-AlN (1.5 nm) layer.

composition would allow for the more effective creation of an etch stop, as shown in Fig. 2.6(c).

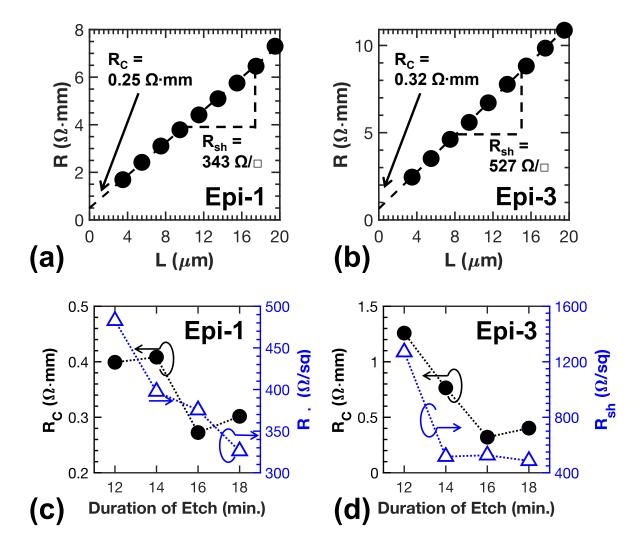

Significant optimization was required to realize the proposed SA p-GaN-gate process, as illustrated in Fig. 2.7(a). The use of a Ni/Au/Ni metal stack allows for, (1) the top Ni to serve as the hard mask for gate definition; (2) the reduction of gate sheet resistance from 10  $\Omega/\Box$  (W only) to < 0.5  $\Omega/\Box$  (this work). It was found to be difficult to deposit the entire W/Ni/Au/Ni stack using a single evaporation and lift-off step. Therefore, two metal deposition steps were required. Two aspects are critical for the gate module, namely (1) a highly selective GaN/AlGaN etch with good surface morphology after etch; (2) highly robust etch mask using gate metal for the etch in (1). Fig. 2.7(b) presents short-loop tests of GaN/AlGaN selective etch, which indicate > 10: 1selectivity and rms roughness of 6 nm. Next, the top metal mask was integrated with this selective etch recipe. Careful optimization was required to the etch conditions and mask. A poor etch would result in significant re-deposition of particles around the gate structure (Fig. 2.7(c)). Furthermore, considering the degradation of the gate structure (Fig. 2.7(d)), such a transistor would require greater access region lengths ( $L_{GS}$  and  $L_{GD}$ ) than what is required for lithography alignment tolerance of the ohmic contacts (as is the case of a standard HEMT). The optimized gate structure is presented in Fig. 2.7(e)–(f). A 80 nm-thick layer of Ni was required in order to ensure sufficient etch resistivity against both F-based and Cl-based plasmas.

### 2.4.2 Results and Discussion

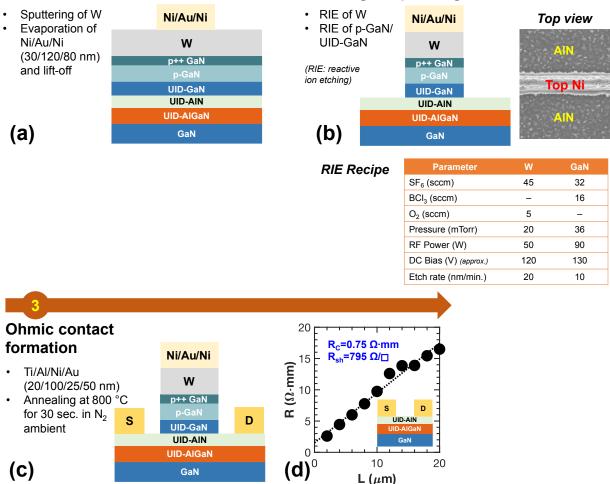

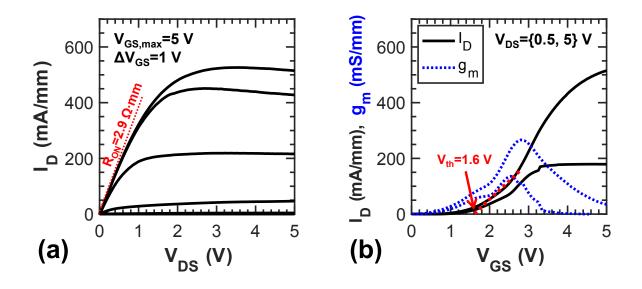

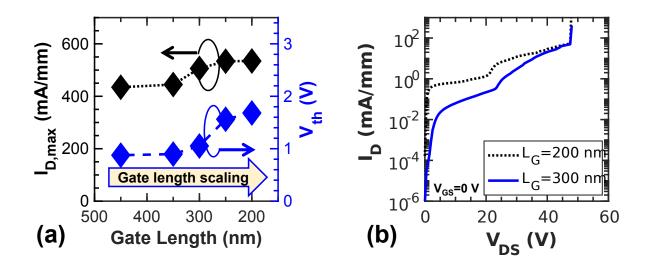

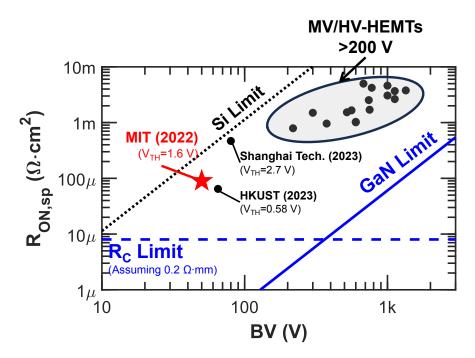

Scaled n-FETs with  $L_G = 200$  nm,  $L_{SD} = 1.1 \,\mu\text{m}$  show good current saturation with  $I_{D,max} = 525$  mA/mm,  $R_{ON} = 2.9 \,\Omega$ ·mm (Fig. 2.8(a)). E-mode operation with  $V_{th} \approx 1.6$  V was achieved (Fig. 2.8(b)). A peak  $g_m$  of 265 mS/mm reflects good gate control using the proposed gate metallization stack. As expected, gate length scaling improves  $I_{D,max}$  for the ON-state characteristics, but slightly worsens the gate control in the OFF-state breakdown measurements. The destructive breakdown was  $\sim 50$  V. It should be noted that, none of the transistors in this work feature any electric field management structures (e.g. field plates, charge balancing [93]), which are expected to push the boundary of the  $R_{ON,SP} \times$  BV trade-off. ( $R_{ON,SP}$  is normalized by area, also known as  $R_{ON} \times A$ .)

Figure 2.7: Details of fabrication optimization of n-FET (p-GaN-gated AlGaN/GaN HEMT), with particular attention on the novel SA p-GaN-gate. (a) Device structure after the formation of the SA p-GaN-gate. (b) Selective etch of p-GaN over AlGaN using a  $BCl_3/SF_6$  process. The inset illustrates the morphology of the etched surface showing an rms roughness of 6 nm. (c) Optical image of a gate region (but with thin top Ni mask), showing that significant amounts of metal was sputtered off the gates. (d) SEM image of a gate with a non-ideal etch. (e)–(f) Optical and SEM images of a gate region with optimized etch, respectively. The region around the gate metal was clean.

Figure 2.8: Performance of n-FET with  $L_G = 200$  nm,  $L_{SD} = 1.1 \,\mu\text{m}$  fabricated on Epi-1. (a) Output characteristics, showing  $R_{ON} = 2.9 \,\Omega$ ·mm and good current saturation with  $I_{D,max} = 525$  mA/mm (calculated at  $V_{GS} = 5$  V). (b) Transfer characteristics, showing  $V_{th} = 1.6$  V and peak  $g_m = 265$  mS/mm.

Figure 2.9: Gate length scaling of SA p-GaN-gate n-FETs (Epi-1). (a) ON-state characteristics.  $\sim 40$  transistors fabricated in the same batch were studied. (b) OFF-state characteristics, without any electric field management structures (e.g., field plate). In these transistors,  $L_{GS} = L_{GD} = 450$  nm.

As shown in Fig. 2.9, the impact of gate length scaling on the SA p-GaN-gate n-FETs was studied. In terms of ON-state characteristics, gate length scaling improves  $I_{D,max}$ . Furthermore, it is observed that  $V_{th}$  becomes more positive (E-mode) for scaled  $L_G < 250$  nm. In terms of OFFstate characteristics, a slightly longer  $L_G$  improves gate control and reduces leakage current before destructive breakdown (at ~ 50 V). It should be noted that, none of the transistors in this work feature any electric field management structure.

The maximum achievable  $I_D$  in the W/p-GaN-gate HEMTs is typically limited by (1) the allowable gate overdrive before the onset of significant gate leakage; (2) carrier velocity in scaled transistors. Through analysis of temperature-dependent current-voltage characteristics from room temperature to 500 °C, it was found that the gate current in the reverse bias and onset of forward bias is dominated by two-dimensional variable range hopping (2D-VRH), while the gate current in the strong forward bias regime is dominated by the leakage through the vertical junction current. A detailed analysis of the gate leakage of such W/p-GaN-gate HEMTs (including temperature dependency) is reported in [94].

# 2.4.3 Comparison of n-FETs based on the GaN-CMOS platform and a conventional p-GaN epitaxy

As mentioned in Sect. 1.3, there are some noticeable differences between the GaN-CMOS platform and the conventional p-GaN HEMT epitaxy. While the exact epitaxial design of commercially available p-GaN-HEMTs are not publicly known, a conventional p-GaN HEMT epitaxy (Fig. 1.2(a), p-GaN (70 nm)/AlGaN (15 nm)/GaN, "Epi-2") was used for this experiment. While the scaled SA p-GaN-gate n-FET technology was originally developed for integration with p-FETs on the GaN CMOS platform, it could also be useful in its own in low-voltage GaN power ICs or GaN n-FET-only logic. To evaluate the robustness of this technology for such a possibility, the same process flow was applied on a conventional p-GaN-gate epitaxial structure. It should be noted that, previous efforts have been made to fabricate p-FETs on Epi-2 [95].

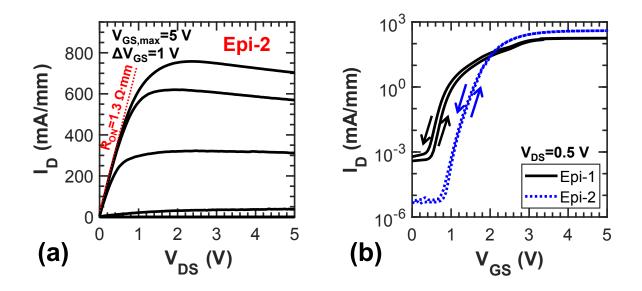

In the n-FETs based on Epi-2, better performance ( $I_{D,max} = 750 \text{ mA/mm}, R_{ON} = 1.3 \Omega \cdot \text{mm}$ ),

Figure 2.10: Performance of n-FET fabricated on Epi-2. (a) Output characteristics, showing  $R_{ON} = 1.3 \ \Omega$ ·mm and good current saturation with  $I_{D,max} = 750 \text{ mA/mm}$  (calculated at  $V_{GS} = 5 \text{ V}$ ). (b) Comparison of the performance of n-FETs based on Epi-1 and Epi-2.

higher current ON-OFF ratio (Fig. 2.8(c)), sharper ON-OFF transition (SS values of n-FETs based on Epi-1 and Epi-2 are 123 mV/dec and 100 mV/dec, respectively), and negligible hysteresis (< 0.1 V)) (Fig. 2.8(d)) were observed. The above improvements with respect to the n-FET in the CT platform are attributed to the location of the gate metal closer (by  $\sim 25$  nm) to the n-channel at the AlGaN/GaN interface, and better gate electrostatic control by the metal gate to the n-channel (absence of UID-GaN and AlN, thinner AlGaN layer).